# CCDイメージセンサ

#### 目次

構造、動作原理

1-1 CCDの種類 1-2 電荷転送動作

1-3 FDA

**1-4** 信号電荷のビニング

1-5 信号電荷の注入

1-6 NMOSイメージセンサとの比較

1-7 表面入射型/裏面入射型CCD

1-8 近赤外高感度タイプ裏面入射型CCD

マルチポートCCD

1-10 電子冷却型CCD

1-11 TDI-CCD

1-12 レジスティブゲート構造

1-13 埋め込み型フォトダイオード

特性 2.

<u>P.12</u> 2-1 変換係数

2-2 分光感度特性

2-3 窓材の選択

2-4 感度不均一性

2-5 飽和電荷量

2-6 直線性

2-7 電荷転送効率

2-8 暗電流 2-9 ノイズ

2-10 ダイナミックレンジ

2-11 解像度

2-12 点像分布関数 (point spread function)

2-13 ノイズの周波数特性

2-14 スプリアスチャージ

アンチブルーミング

2-16 電子シャッタ

2-17 エタロニング

2-18 コスメティックス

**2-19** 宇宙線によるCCDへの影響

₹3. 使い方

<u>P.23</u> 3-1 タイミング

クロックパルス、DCバイアスの調整

3-3 信号処理回路

3-4 高速信号処理回路

3-5 出力回路における発光の対策

3-6 チップ温度

補正

3-8 FOSとのカップリング

3-9 放射線損傷

3-10 放熱

3-11 静電気/サージ対策

4. 応用製品

<u>P.35</u> 4-1 特長

構成

4-3 使い方

新たな取り組み 5.

P.37

# 構造、動作原理

CCDイメージセンサ [以下CCD: Charge Coupled Device]は、1970年にAT&Tベル研究所のBoyleと Smithにより考案されたデバイスです。CCDは、電荷転 送デバイス (CTD: Charge Transfer Device)の1つであ り、ポテンシャルウェル (potential well: 電位の井戸)を 利用して半導体中で電荷を転送するイメージセンサで す。今日では、ほとんどのCCDで基板内部に電荷転送路 が埋め込まれたBCCD (Buried-channel CCD)構造が 使われています。

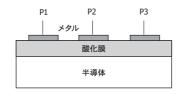

CCDのポテンシャルウェルは、図1-1に示すように複数 のMOS (Metal Oxide Semiconductor)構造の電極の1 つに他と異なる電圧を加えることによって実現されます。

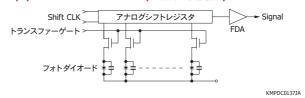

ポテンシャルウェルに閉じ込められた信号電荷は、半導 体中を出力部に向かって順次転送されます。したがって CCDは、アナログシフトレジスタとも呼ばれています。

このようにCCDは、半導体中で電荷を転送するデバイ スですが、現在ではイメージセンサとして広く一般に使 用されているため、イメージセンサやカメラの代名詞とし ても呼ばれるようになっています。

#### [図1-1] CCDの基本構造とポテンシャルウェル

KMPDC0036JE

# 1-1 CCDの種類

現在、実用化されているCCDは、転送方式によって以下の4つに分類されます。

- ・FT (Frame Transfer)型 (2次元)

- ・FFT (Full Frame Transfer)型 (2次元)

- ・IT (Interline Transfer)型 (1次元、2次元)

- ・FIT (Frame Interline Transfer)型 (2次元)

FFT型・1次元型以外のタイプは、汎用のビデオカメラに使用されています。FFT型・1次元型は、動作原理上ビデオカメラに利用することは難しく、主として計測用や分析用に利用されています。

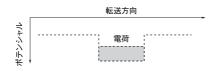

#### (1) FT型

FT型CCD (FT-CCD)は、受光部と蓄積部から成る2つの垂直シフトレジスタと1つの水平シフトレジスタおよび出力部より構成されます。垂直シフトレジスタはパラレルレジスタ、水平シフトレジスタはシリアルレジスタまたは読み出しレジスタと呼ばれることもあります。受光部の電極としては、一般的にPoly-Si (多結晶Si)などの透明電極を使用します。

透明電極を通ってCCDの半導体中に光が入射すると、光電変換が行われ信号電荷が発生します。この信号電荷は、特定の蓄積時間に電極下のポテンシャルウェルに集められます。その後、信号電荷は、垂直帰線期間を利用してフレームごと蓄積部に高速転送されます。このようにFT型では、受光部の垂直シフトレジスタは、蓄積時間において光電変換デバイスとして機能します。

蓄積部の信号電荷は、受光部で光電変換と信号の蓄積が行われる間に、水平シフトレジスタを通って出力部に転送されます。この動作は、蓄積部の1ラインごと水平帰線期間に水平シフトレジスタへ電荷が転送されることによって行われます。なおFT型の受光部以外の部分は、光が入らないようにアルミなどの不透明金属で覆われています。

#### [図1-2] FT型の構造

KMPDC00373

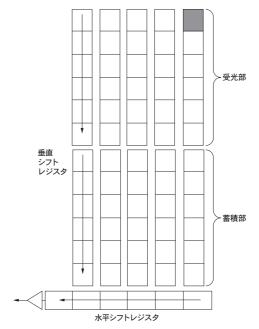

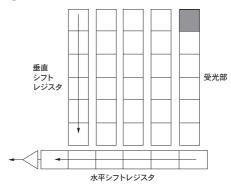

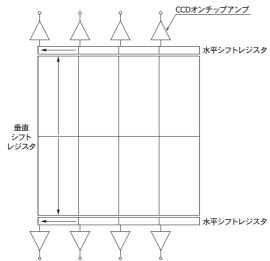

#### (2) FFT型

FFT型CCD (FFT-CCD)は、基本的にはFT型CCDから蓄積部をなくした構成です。蓄積部がないために、通常は何らかの外部のシャッタ機構と併用して使用されます。この制約のため、ビデオカメラに使用することは難しい構成になっています。

動作原理はFT型に似ており、蓄積時間には受光部のポテンシャルウェルに電荷を集め、シャッタの閉期間などに水平シフトレジスタを通して信号電荷が出力部に転送されます。

FFT型は、蓄積部がないため同一のチップサイズで画素数を多くしたり、画素サイズを大きくできるため、主としてフレームレートの遅い計測用のカメラシステムに使用されます。なお、当社製のCCDの多くはFFT型です。

#### [図1-3] FFT型の構造

KMPDC0038JA

#### (3) IT型

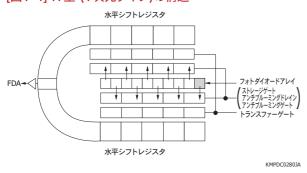

#### ■ 1次元タイプ

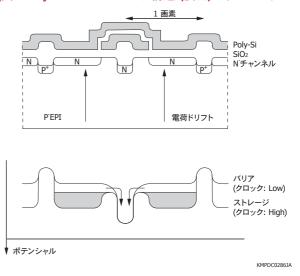

IT型CCD (IT-CCD)の1次元タイプでは、フォトダイオードで光電変換により発生した信号電荷は、隣接したストレージゲートに集められます。その後、ストレージゲートと水平シフトレジスタの間にスイッチとして設けられたトランスファーゲートを通して、水平シフトレジスタに信号電荷が転送されます。ストレージゲートから水平シフトレジスタへの転送は、全画素について同時に行われます。

図1-4に、IT型CCD (1次元タイプ)の構造を示します。フォトダイオードアレイの奇数画素の信号電荷は上の水平シフトレジスタへ、偶数画素の信号電荷は下の水平シフトレジスタへ転送され、1つのFDA (Floating Diffusion Amplifier,「1-3 FDA」参照)で交互に信号電荷が検出されます。奇数画素と偶数画素の信号電荷を別々の水平シフトレジスタへ転送することによって、フォトダイオードアレイの小ピッチ化や、アンチブルーミングや電子シャッタの構造を形成することが可能になります。

#### [図1-4] IT型 (1次元タイプ)の構造

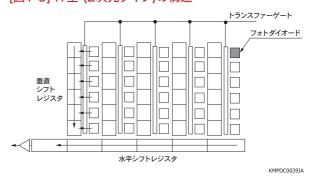

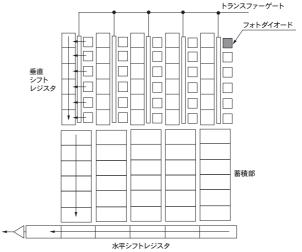

#### ☑ 2次元タイプ

IT型CCD (2次元タイプ)では、受光部は、フォトダイオードかMOS構造のダイオードで成り立っており、転送部とは別に設けられています。最近のIT型 (2次元タイプ)では、暗電流の少ない埋め込み型フォトダイオードが用いられています。垂直シフトレジスタはフォトダイオードの横に配置され、さらに水平シフトレジスタと出力部により構成されます。

フォトダイオードで光電変換により発生した信号電荷は、フォトダイオード自身の接合容量などに集められます。その後、垂直帰線期間に、フォトダイオードと垂直シフトレジスタの間にスイッチとして設けられたトランスファーゲート(転送ゲート)を通して、垂直シフトレジスタに信号電荷が転送されます。この動作はFT型とはやや異なり、IT型(2次元タイプ)のフォトダイオードから垂直シフトレジスタへの電荷の転送は、全画素について同時に行われます。

この後の動作は、FT型の「蓄積部への信号電荷の転送」以降の動作と同じであり、信号電荷は水平帰線期間に1ラインずつ水平シフトレジスタへ転送され出力されます。

図1-5にIT型 (2次元タイプ)の構造を示します。FT型 と同様にフォトダイオード以外の部分は、アルミなどによって遮光されています。IT型 (2次元タイプ)では、信号 電荷の蓄積部から出力部への転送は、フォトダイオード が蓄積動作を行っている期間を利用して行われます。このため、垂直シフトレジスタへの信号電荷の漏れ込みによるスミアと呼ばれる現象が発生しやすくなっています。

#### [図1-5] IT型 (2次元タイプ)の構造

#### (4) FIT型

FIT型CCD (FIT-CCD)は、IT型CCDの問題点を改善するために考案されたタイプで、IT型に蓄積部を設けた構成になっています。FIT型では、フォトダイオードから垂直シフトレジスタへ信号電荷が転送されると、すぐに蓄積部に信号電荷が高速転送されます。したがってFIT型には、IT型に比べてスミアを少なくできるという特長があります。

#### [図1-6] FIT型の構造

KMPDC0040JA

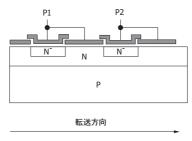

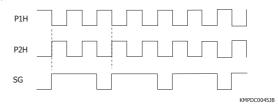

# 1-2 電荷転送動作

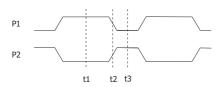

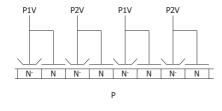

1画素を2本の電極 (gate)で構成したCCDを2相CCD または2電極CCDと呼びます。2相CCDでは、2つの異なる電圧レベル (Highレベル、Lowレベル)をもったクロックパルスを加えることによって [図1-7 (c)]、信号電荷の転送が行われます。

2相CCDでは、半導体プロセスによって作成した電位 差により信号電荷の転送方向が決まります。信号電荷 は、蓄積電極下に蓄積されます。たとえば図1-7の場合、 時刻 t1ではP1電極をHighレベル(P2電極はLowレベ ル)にすることで、信号電荷はP1電極の蓄積電極下に蓄 積されます。

2相CCDでは、クロックパルスのオーバーラップが重要です。タイミングチャート [図1-7 (c)]に示すように、P1・P2がHighレベルとLowレベルの中間よりも高いレベル (HighレベルをV、Lowレベルを0としたとき、V/2以上のレベル)で交差する必要があります (時刻 t2)。P1がHighレベルのときにP2がLowレベルになるような状態が交互に切り替わるように設定することで、信号電荷を転送することが可能になります。

#### [図1-7] 2相CCDの動作原理

#### (a) 構造

#### (b) 電位

#### (c) タイミングチャート

KMPDC0042JB

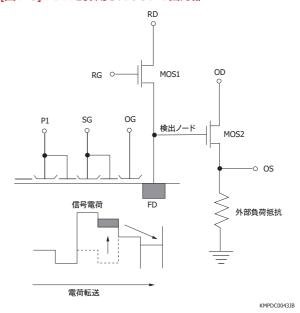

### 1 - 3 FDA

FDA (Floating Diffusion Amplifier)は、最も広く使用されている「CCDの電荷検出の方式」です。FDAは、図1-8に示すように電荷の検出ノードと、それに接続されたリセット用MOSFET (MOS1)と電荷-電圧変換用MOSFET (MOS2)により構成されます。検出ノードに転送された電荷は、電荷-電圧変換用MOSFETで、Q=CVの関係により電荷から電圧に変換されます。次の信号を読むために検出ノードは、リセット用MOSFETによりリファレンスレベル (RDの電圧)にリセットされます。

FDAでは、検出に伴うノイズはノードの容量によって決まりますが、Whiteによって提案されたCDS (Correlated Double Sampling: 相関2重サンプリング)によってほとんど除去することができます。

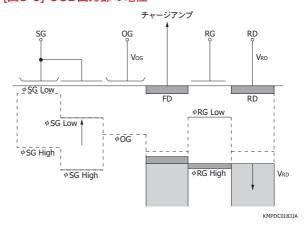

信号電荷が出力されるタイミングは、シフトレジスタの 最終クロックゲートであるサミングゲート (SG)がHighレ ベルからLowレベルになるときと同期しています。

#### [図1-8] FDAを採用したCCDの出力部

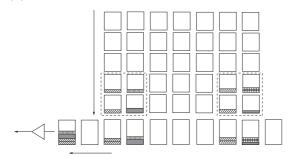

# 1-4 信号電荷のビニング

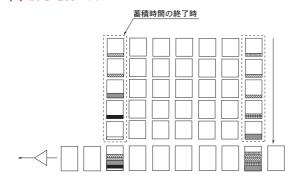

CCDの信号電荷は、蓄積時間にそれぞれの画素のポテンシャルウェルに蓄積されます。FFT型CCDでは、蓄積時間の終了時には、図1-9 (a)に示すように2次元的に情報が蓄えられています。

垂直のシフトレジスタと水平のシフトレジスタは個別にクロックパルスを入れることができるため、ビニングと呼ばれる動作方法が可能です。ビニングはCCD特有の動作方法で、信号電荷を加算する方向によってライン(垂直)ビニングとピクセル(水平)ビニングに分けられます。

#### (1) ラインビニング (line binning)

ラインビニングでは、縦方向の画素の信号を加算します。図1-9 (b)に示すように、水平シフトレジスタのクロックパルス P1Hを停止した状態で垂直シフトレジスタに所定の回数のクロックパルス P1V・P2Vを入れると、信号電荷は対応する水平シフトレジスタの1画素に次々に転送され信号が加算されます。

ラインビニングを用いることによって、縦方向に非常に長い受光領域をもった1次元センサと同等の信号を得ることができ、さらに出力部における読み出しが一度で済むため、読み出しに伴うノイズの混入を最小限にすることができます。

#### [図1-9] ラインビニング

#### (a) 信号電荷の流れ

#### (b) タイミングチャート

#### (2) ピクセルビニング (pixel binning)

CCDの水平シフトレジスタの最終ゲートは、サミングゲート(SG)と呼ばれる単独のゲートで構成されています。ピクセルビニングを行わない場合には、SG端子を直接P2Hと短絡することによって使用できます(SGをP2Hと短絡しないで、P2Hと同じクロックパルスを入れても構いません)。SGに別のクロックパルスを入れることによって、ピクセルビニングが可能になります。

ラインビニングと組み合わせて使用することで、図1-10 に示すように2 × 2画素などの信号を加算することができます。この場合、まずラインビニングによって2ラインの信号が水平シフトレジスタの画素に加算されます。次に、水平シフトレジスタによる信号電荷の読み出しにおいて、P1Hの2クロックパルス期間に1クロックの割合でSG端子にクロックパルスを入れることで、SGにおいて水平の2つの画素の信号を転送して加算することができます。

この方法を用いれば、たとえば1024 × 1024画素の CCDにおいて入射光量が十分でないとき、512 × 512画 素のセンサとして機能させることによって、解像度は低下しますが、コントラストの優れた画像を得ることができます。

#### [図1-10] ピクセルビニング

#### (a) 信号電荷の流れ

#### (b) タイミングチャート

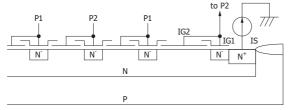

## 1-5 信号電荷の注入

CCDには、電気的な信号入力テスト端子として、垂直シフトレジスタと水平シフトレジスタの先頭に入力ソース(ISV, ISH)と入力ゲート(IGV, IGH)が配置されています。通常は、これらのテスト端子には一定のバイアス(データシート参照)を印加しておきますが、入力ソースと入力ゲートに既定値以外のバイアスやクロックパルスを加えることでシフトレジスタに信号電荷を注入することができます。これによって、放射線によるCCDの電荷転送効率の劣化を低減することができます。また、飽和電荷量やFDAの直線性を定量的に評価するためにも利用できます。入力ソースに電流源を接続し、入力ゲートをP2と短絡してクロックパルスを入れることで、シフトレジスタに信号電荷を注入できます [図1-11]。この方法における注入電荷量は、電流源の注入電流値と注入時間(CCDの駆動周波数の逆数に相当)の積に一致します。

$Qinj = Iinj \times t \cdots (1-1)$

Qinj: 注入電荷量 [C] Iinj: 注入電流 [A] t : 注入時間 [s]

#### [図1-11] 電流源を接続した信号電荷注入部の構造

KMPDC0136JE

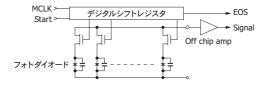

# 1-6 NMOSイメージセンサとの比較

CCDイメージセンサとNMOSイメージセンサは、方式 が異なるため仕様や性能が大きく異なります。

NMOSイメージセンサは、フォトダイオードに蓄積された信号電荷をデジタルシフトレジスタにより順次アドレスすることで、スイッチのMOSFETを通して信号ラインに電荷を出力します。このとき、デジタルシフトレジスタにTTLレベルの一定のタイミングのクロックパルスを供給すれば動作するため、外部の信号処理部を除けば5 V単一電源で動作させることができます。

一方、CCDイメージセンサ(1次元IT型)の場合、フォトダイオードに蓄積された信号電荷は、スイッチのMOSFETをオンにすることでアナログシフトレジスタに転送されます。その後、信号電荷はアナログシフトレジスタにより、順次、最終に設けられたFDAに転送され出力されます。CCDイメージセンサは、動作に必要な電源は単一ではなく、クロックパルスは仕様に定められた所定の振幅にする必要があります。CCDイメージセンサは、読み出しノイズレベルが数~十数e・rmsと小さく、また、FDAを構成するアンプの帯域により、10 MHzを超える画素レートでの読み出しが可能になります。

NMOSイメージセンサは、ノイズが3000 e-rmsと大きいですが、取り扱い可能な信号電荷量がCCDイメージセンサの数十万e-に比べて100倍以上も大きいため、一般に検出する光が十分に大きい場合にはNMOSイメージセンサを使った方が簡易なシステムが実現できます。一方CCDイメージセンサは、ノイズが小さいため、NMOSイメージセンサで検出できない光でも十分なS/Nが得られ、微弱光検出に適しています。

#### [図1-12] NMOS/CCDイメージセンサの比較

#### (a) NMOSイメージセンサ

#### (b) CCDイメージセンサ (IT型、1次元型)

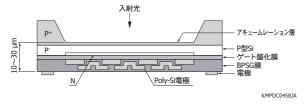

## 1-7 表面入射型/裏面入射型CCD

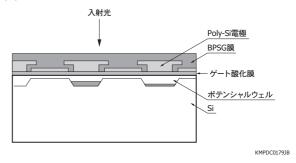

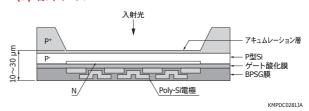

一般的にCCDは、パターンが形成されている側から 光を入射させる構造になっています。このような構造の CCDを表面入射型CCDといいます。表面入射型CCDの 光入射面は、BPSG膜・Poly-Si電極・ゲート酸化膜など が堆積したSi基板の表面にあるため、入射光はその部 分で大きく反射・吸収されます [図1-13 (a)]。このため 量子効率は可視域で最大40%程度になり、紫外域には 感度がありません。

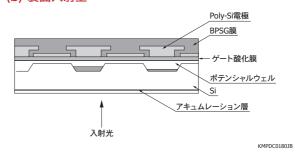

このような問題を解決するために開発されたのが裏面入射型CCDです¹)。裏面入射型CCDは、BPSG膜・Poly-Si電極・ゲート酸化膜などがないSi基板の裏面から光を入射する構造になっています[図1-13 (b)]。このため裏面入射型CCDは、広い波長域で高い量子効率を実現します。裏面入射型CCDは、CCDが本来もっている高感度・低ノイズといった特長をそのまま生かした上に、電子線・軟X線・紫外・可視・近赤外域に感度をもっています。

#### [図1-13] CCDの概念図

#### (a) 表面入射型

#### (b) 裏面入射型

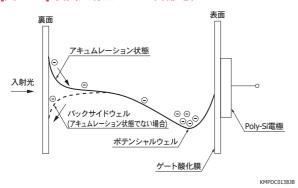

裏面入射型CCDの高感度を実現するためには、Si基板の薄型化と受光面の活性化が不可欠です。受光面の活性化は、裏面入射面近くで発生した信号電荷が、再結合せずに入射面からCCDのポテンシャルウェルまでスムーズに運ばれるように内部電位の勾配を形成すること(アキュムレーション)によって行われます<sup>2)3)</sup>。アキュムレーション状態の内部電位の様子を図1-14に示します。

#### [図1-14] 裏面入射型CCDの内部電位

裏面入射型CCDを光入射方向から見た場合、水平シフトレジスタはSiの厚い部分(不感部分)で覆われており、短波長の光はほとんど水平シフトレジスタに到達することはありません。しかし、長波長の光は不感部分のSiを透過し、水平シフトレジスタで受光される可能性があります。

外部シャッタを使用しない場合、電荷の蓄積中や転送中にも水平シフトレジスタに光が入り、その信号は偽信号として実際の信号に重畳されます。たとえば、時間的に変化のない信号が水平シフトレジスタに入射する場合、信号に一定のオフセット上昇として現れます。その影響は水平転送時間が短いほど小さくなります。

必要に応じて、外部シャッタの使用、光入射位置の調整、遮光などの対策を行ってください。

[図1-15] 裏面入射型CCDのデバイス構造 (外形寸法図において上面から見たCCDチップ概念図)

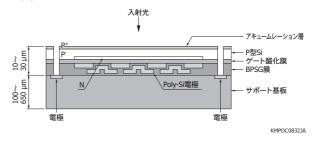

# 1-8 近赤外高感度タイプ裏面入射型CCD

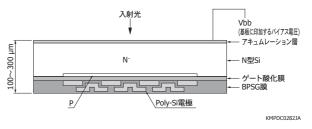

通常の裏面入射型CCDは、紫外/可視域で高い量子 効率をもっていますが、Si厚が15~30 μm程度のため近 赤外域の量子効率は低く、波長 1 μmの量子効率は約 20%です。Siを厚くすれば近赤外域の感度は向上します が、中性領域(空乏化していない領域)における電荷が横 方向に拡散することにより、解像度が劣化してしまいます。

このような問題を解決するために開発されたのが近 赤外高感度タイプ裏面入射型CCDです。近赤外域で高 感度を実現するために、以下の完全空乏化タイプを用意 しています。

#### ◊ 完全空乏化タイプ

完全空乏化タイプは、空乏層を厚くするために超高抵抗のN型ウエハを使用しています。Siの比抵抗が同じ場合、N型ウエハはP型ウエハよりも不純物濃度を低くでき、同じバイアス電圧でも厚い空乏層にすることができます[図1-16(b)]。一方、裏面にバイアス電圧を印加することでMPP動作(「2-8 暗電流」参照)ができないこととSiが厚いことから暗電流が大きくなり、-70~-100°Cに冷却する必要があります。なお、標準タイプの裏面入射型CCDはSi厚が薄いため大面積化は困難ですが、完全空乏化タイプ裏面入射型CCDはSi全体を100~300 μm程度に厚くするため、大面積化を容易に行うことができます。

#### [図1-16] 裏面入射型CCDの内部構造

#### (a) 標準タイプ

#### (b) 完全空乏化タイプ

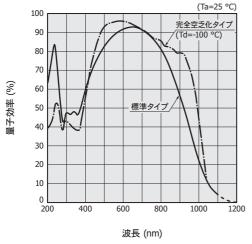

#### 「図1-17」 分光感度特性 (裏面入射型CCD, 窓なし時, 代表例)

KMPDB0295JD

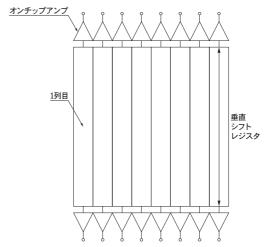

# 1-9 マルチポートCCD

CCDの読み出し時間は、画素数と読み出し周波数によって決まり、長い時間を必要とします。たとえば1024×1024画素で読み出し周波数 100 kHzの場合には、読み出し時間だけで10秒以上がかかります。

読み出し周波数と読み出しノイズは、トレードオフの関係にあります。読み出し周波数を高くすると、読み出し時間は短くなりますが読み出しノイズは大きくなってしまいます「図2-18」。

CCDのアンプを複数にすること (マルチポート化)で、 画素の読み出しを並列化してフレームレート (1秒当たり に取得できる画面数)を向上させることができます。

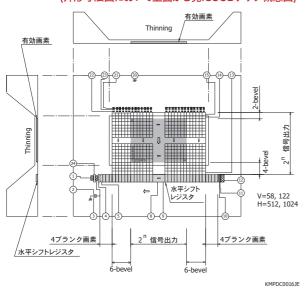

#### 「図1-18] マルチポートCCDの構造

KMPDC01403A

マルチポートCCDを進化させて画素の読み出しをさら に高速化したものが列並列型CCDです。画素1列ごとに オンチップアンプを設けて、各オンチップアンプを垂直シ フトレジスタと接続した構造をもちます。列並列型CCDに は水平シフトレジスタがなく、水平シフトレジスタの転送 時間がかからないため、従来のマルチポートCCDを超え る高速応答を実現することが可能です。

なお、列並列型CCDではオンチップアンプ数が非常に多くなるため、信号処理回路を外部に設けることは実用的ではありません。当社は、オンチップのCMOS信号処理回路を搭載したTDI-CCDを開発しました(「1-11 TDI-CCD (参照)。

#### [図1-19] 列並列型CCDの構造

KMPDC0844JA

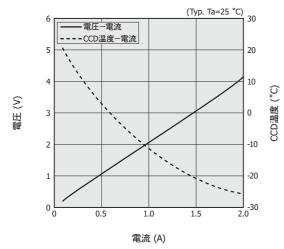

# 1 - 10 電子冷却型CCD

CCDの暗電流は温度特性をもち、CCDの温度が5~7°C下がるごとに約半分になります。このためCCDを冷却することは、MPP動作(「2-8暗電流」参照)と並んで暗電流を低減して検出限界を改善する効果的な方法です。

電子冷却型CCDにおいて、パッケージに内蔵された電子冷却素子(ペルチェ素子)によってCCDの冷却を行います。冷却温度は、電子冷却素子の最大吸熱量や放熱能力によって決まります。電子冷却素子は、製品によって以下の値が異なります。

- ・最大電流 (Imax)

- ・最大電圧 (Vmax)

- ・最大吸熱量 (Qmax)

電子冷却素子やCCDを破損しないためには、データシートに記載された数値の範囲内で使用してください。電子冷却素子の使用に当たって、放熱の方法は重要です。放熱が十分に行われない場合、期待した冷却ができないことがあります。これは、高温側の温度上昇が起きるためであり、放熱器の最適化や強制空冷/水冷などが必要になります。なお電子冷却素子は、最大電流値の60%以下で使用することによって効果的にCCDを冷却できます。

周囲温度 25°Cの場合、CCDは以下の温度に冷却されます。

- ·1段電子冷却型:0~-10°C位

- ·2段電子冷却型: -20~-30°C位

- ·4段電子冷却型: -50~-70°C位

安定した動作を実現するために、周囲環境に合わせ て電子冷却素子の電流や放熱条件を決める必要があ ります。

#### [図1-20] 1段電子冷却素子の特性 (S7171-0909-01)

KMPDB01803/

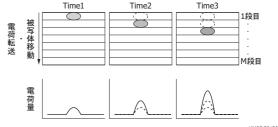

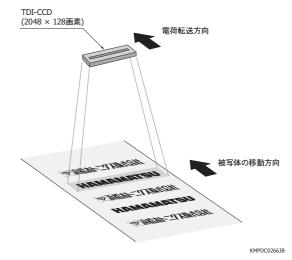

## 1-11 TDI-CCD

裏面入射型TDI (Time Delay Integration)-CCDは、高速撮像時などにおいて低照度下でも高いS/Nの画像が得られるCCDです。TDI動作により、移動する対象物を積分露光することで、飛躍的に高い感度を得ることができます。裏面入射型のため、紫外〜近赤外の幅広い波長域 (200〜1100 nm)で高い量子効率を実現しています。

#### ◆ TDI動作

CCDでは、ポテンシャルウェルに信号電荷を保持して、個々の電荷が混じらないように転送して出力します。 TDI動作は、このようなCCDの電荷転送の原理を巧みに利用して、微弱光を検出したり、移動する物体を撮影したり、あるいはCCDセンサ自体が移動して、静止物体をスキャンして撮影する場合に有効な方法です。

通常、センサ上に結像された画像は、その位置に対応した信号量として出力されます。この方法では、蓄積時間の間に結像された画像は必ず同じ位置にあることが必要であり、何らかの理由で結像位置にずれが生じると画像のS/Nが低下します。被写体が移動する場合、結像位置がずれることで画像にボケが発生し、場合によってはまったく画像にできないこともあります。

それに対してTDI動作は、移動する被写体に対しても画像化できるユニークな動作方法です。FFT型CCDでは、電荷読み出しの際、列単位で電荷の垂直転送を行います。その転送のタイミングと被写体の移動タイミングを合わせ、CCD画素の垂直段数分の回数で信号電荷の蓄積をする方式がTDI動作です。

TDI動作においては、被写体の移動と同じ方向に同じ 速度で電荷転送を行う必要があります。その速度は、式 (1-2)で表されます。

$v = f \times d \cdots (1-2)$

- v: 被写体移動速度、電荷転送速度

- f: 垂直の転送周波数

- d: 画素サイズ (転送方向)

図1-21の1段目で蓄積された電荷が2段目に転送されるのと同時に2段目においても光電変換により電荷の蓄積が行われます。この動作をM段(垂直段数)まで連続して行った場合には、M倍の電荷が蓄積されます。このため、リニアイメージセンサに比べてM倍の感度を実現できます(垂直段数が128の場合、通常のリニアイメージセンサに比べて128倍の感度が得られます)。蓄積された電荷はCCDの水平シフトレジスタから列ごとに出力され、とぎれがない2次元の画像が得られます。またTDI動作では、2次元動作モード時よりも感度のバラツキが改善されます。

#### 「図1-211 TDI動作による積分露光の模式図

KMPDC0139JA

#### [図1-22] TDI動作による撮影例

#### (a) 高速移動する対象物の撮影

#### (b) 高速回転する対象物の撮影

KMPDC02671A

図1-22 (b)においてCCDを2次元動作させてドラムが 静止した状態で撮影した場合、図1-23 (a)のようにブレ のない画像を取得することができますが、ドラムが回転 していると図1-23 (b)のように画像はブレてしまいます。 シャッタ時間を短くした場合、ブレのない画像が得られま すが、画像は図1-23 (c)のように暗くなります。TDI-CCD は、ドラムの回転と同じ方向に同じ速度で電荷転送を行 うため、図1-24のような明るくブレのない連続画像が得 られます。

#### [図1-23] 2次元動作による撮影

(a) ドラム静止時

#### HAMAMATSU

(b) ドラム回転時

(c) ドラム回転時 (シャッタ時間を短くした場合)

#### [図1-24] TDI動作による撮影 (ドラム回転時の連続画像)

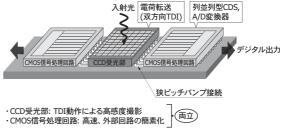

#### ◆ CMOS信号処理回路付TDI-CCD

高速撮影時において十分な明るさの画像が得られる TDI-CCDと、デジタル出力を可能にするCMOS信号処理 回路の特長を併せもった新しいイメージセンサも用意し ています。

従来のTDI-CCDはアナログ出力のため、外部に信号 処理回路を用意する必要がありました。CMOS信号処 理回路付TDI-CCDは、オンチップのCMOS信号処理回 路を搭載することによりA/D変換後にデジタル信号を出 力するため、外部回路の簡素化が可能です。図1-25に 構成を示します。受光・電荷転送を行うCCD受光部と CMOS信号処理回路のそれぞれを最適なプロセスで製 造して組み合わせることによって、最良の特性が得られ ます。これによりCMOS信号処理回路付TDI-CCDは、紫 外域における高い感度や高い電荷転送効率など、従来 のTDI-CCDの特長を損なうことなく、デジタル出力を実 現しています。

また、列並列型CMOS信号処理回路を使用しており、 CCD受光部の列並列読み出しが可能です。出力信号を 外部で処理する従来のTDI-CCDにおいて列並列読み 出しは、外部回路が大型化するため実現が困難でした。 CMOS信号処理回路付TDI-CCDでは簡易な外部回路 にて、高いラインレートを実現します。

#### 「図1-251 CMOS信号処理回路付TDI-CCDの構成 (S14810, S14813)

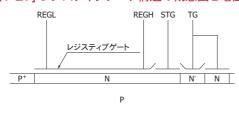

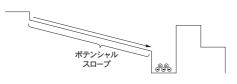

# 1 - 12 レジスティブゲート構造

通常のCCDの場合、1画素内に複数の電極があり、異 なったクロックパルスを印加することで信号電荷を転送 します「図1-26」。レジスティブゲート構造の場合、受光 部に単一の高抵抗電極があり、その両端に異なる電圧 を印加してポテンシャルスロープを形成することで信号 電荷を転送します「図1-27」。CCDエリアイメージセンサ をラインビニングし1次元のセンサとして使用する場合に 比べると、CCDリニアイメージセンサの受光部においてレ ジスティブゲート構造を採用することによって、高速転送 が可能になり、画素高さが大きい場合でも読み残しの少 ない読み出しを行うことができます。

#### 「図1-26] 通常の2相CCDの概念図と電位

KMPDC0320E

#### [図1-27] レジスティブゲート構造の概念図と電位

KMPDC0321JB

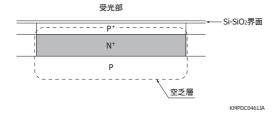

# 1 - 13 埋め込み型フォトダイオード

受光部にフォトダイオード構造を採用した表面入射型CCDリニアイメージセンサ(IT型)において、フォトダイオードを埋め込み型にすることによって低暗電流を実現できます。埋め込み型フォトダイオードは、受光部の表面に薄いP+拡散層を設けたP+N+P構造となっています[図1-28]。空乏層がSi-SiO2界面から離れているため、暗電流をMPP動作時のCCDと同等のレベルまで低減できます。

#### [図1-28] 断面構造 (埋め込み型フォトダイオード)

埋め込み型フォトダイオードの受光部表面には、表面入射型CCDイメージセンサ(FFT型)とは異なりPoly-Si ゲート電極が形成されていません。この構造により、表面入射型であっても紫外域で高い量子効率を実現しています。

#### [図1-29] 分光感度特性 (窓なし時、代表例)

KMPDB0588JB

# 2. 特性

## 2-1 変換係数

変換係数は、FDAが電荷を電圧に変換する割合を示す係数です。

FDAによって信号電荷は、出力端 OSにて電圧  $\Delta$ Vout として出力されます。

$\Delta$ Vout = Av × Q / Cfd ······· (2-1)

Av:電荷-電圧変換MOSFETの電圧ゲイン

Q : 信号電荷 [C] Cfd: ノードの容量 [F]

変換係数 (Sv)は、式 (2-2)で表されます。

$Sv = q \times \Delta Vout / Q [V/e^-] \cdots (2-2)$

q: 1電子当たりの電荷量

S7030/S7031シリーズの場合: Sv=2.2 μV/e-S11071シリーズの場合 : Sv=8.0 μV/e-

ノードの容量 (Cfd)は、式 (2-3)で表されます。

$Cfd = q \times Av / Sv [F] \cdots (2-3)$

S7030/S7031シリーズの場合: Cfd=48 fF S11071シリーズの場合 : Cfd=12 fF

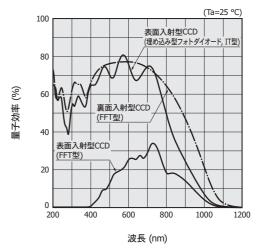

# 2-2 分光感度特性

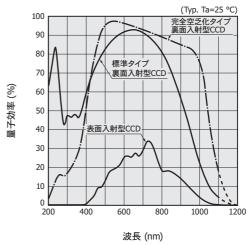

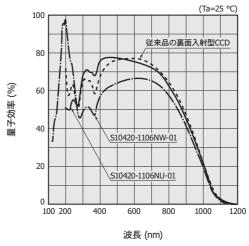

表面入射型CCDと裏面入射型CCDの分光感度特性を図2-1に示します。表面入射型CCDは紫外域に感度がなく、可視域の量子効率のピークは約40%であるのに対し、標準タイプ裏面入射型CCDは紫外域で40%以上、可視域のピークで約90%という非常に高い量子効率を実現しています。完全空乏化タイプ裏面入射型CCDは、Siが厚いため波長800~1100 nmの領域で、標準タイプの裏面入射型CCDよりも高い感度をもっています。また、特殊なARコート形成プロセスを採用することで400~700 nmの可視域でも高い感度をもっていますが、紫外域の感度は低くなっています。

分光感度特性の長波長側は使用するSiの厚さで決まり、短波長側はセンサの光入射面側の構造によって決まります。表面入射型のFFT-CCDでは構造上、有効受光面の上にPoly-Siゲート電極を形成する必要があるため、400 nm以下の紫外域ではほとんど感度がありません。紫外域に感度をもたせるためにCCDにルモゲン(Lumogen)シンチレータをコートしたタイプもあります。裏面入射型CCDは、紫外域から近赤外域まで高い量子効率を実現し、紫外線に対しての安定性も非常に優れています。

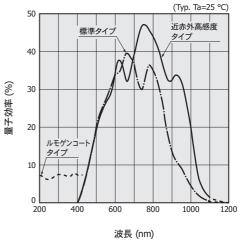

特に700 nm以上の近赤外域において、標準タイプの表面入射型CCDの量子効率は高くありませんが(空乏層の厚さによる)、近赤外高感度タイプ表面入射型CCDは、近赤外域でも高い量子効率を実現しています[図2-2]。

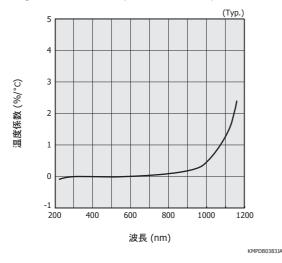

なおCCDを冷却して使用する場合、約800 nm以上の 波長域では感度が低下する方向にシフトするため注意 が必要です [図2-3]。

#### [図2-1] 分光感度特性 (窓なし時)

KMPDB0592JA

#### [図2-2] 表面入射型CCDの分光感度特性 (窓なし時)

KMPDB02053C

#### [図2-3] 感度の温度特性 (S7031シリーズ)

#### (1) 分光感度特性を最適化した裏面入射型CCD

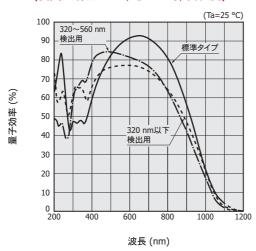

裏面入射型CCDにおいては、受光面上の反射防止膜を最適化することによって、さまざまな分光感度特性を実現することが可能になります[図2-4]。

#### [図2-4] 分光感度特性 (裏面入射型CCD, 窓なし時, 代表例)

KMPDB0593JA

### (2) 紫外域において安定した分光感度特性をもつ 表面入射型CCDリニアイメージセンサ

紫外域に感度をもつ表面入射型CCDの紫外域の分光 感度特性は、素子によってバラツキがありました。当社は、 受光面に特殊な構造を形成することにより、紫外域におけ る分光感度特性の素子ごとのバラツキを抑制した表面入 射型CCDリニアイメージセンサ S11151-2048を開発しま した。

#### (3) ルモゲンコート表面入射型CCD

表面入射型CCDでは、受光面上をPoly-Siの電極が 覆っています。紫外線はPoly-Siによってほとんど吸収さ れてしまい、量子効率はほぼゼロになります。このため 表面入射型CCDは、紫外感度を得るためルモゲンシンチレータをコートする場合があります。ルモゲンは、真空昇華によりCCDの有効受光面上に直接コートされます。

ルモゲンは、480 nm以下の波長の光を吸収して約530 nmを中心に発光します。CCDに入射した紫外線は、ルモゲンシンチレータにより可視光に変換され、この可視光をCCDは検出します。

ルモゲンコート表面入射型CCDは、裏面入射型CCD に比べて紫外線に対する寿命が桁違いに短く、感度の 温度依存性が高いため注意が必要です。

#### (4) 紫外線による感度劣化を抑えた裏面入射型CCD

高照度の紫外線照射時には、感度劣化が問題となります。当社は、製造方法・センサ構造を工夫することにより、紫外線による感度劣化を抑えたCCDを開発しました。従来からの裏面入射型CCDに近い分光感度特性のタイプ(S10420-1106NU-01)、200 nm以下の波長域で高感度を実現したタイプ(S10420-1106NW-01)を用意しています。

#### [図2-5] 分光感度特性 (窓なし時, 代表例)

KMPDB0590JA

## 2-3 窓材の選択

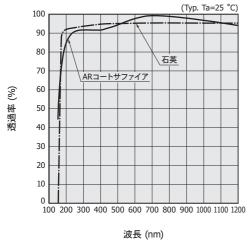

裏面入射型CCDは、最大感度波長の700 nm付近で 量子効率が90%以上になりますが、これは受光窓がな い場合の値です。

CCDの量子効率は、使用する窓材によって影響されます。当社のCCDの窓材としては、AR (反射防止)コート付サファイア (Sタイプ)、石英 (Qタイプ)、窓なし (Nタイプ) の3種が主に使われています。

サファイアは優れた強度をもち、石英に比べて傷つきにくく、高湿環境で安定しています。その上、熱伝導率が金属に近いため結露しにくい、気密封止が可能など、窓材として非常に優れています。ARコートされていないサファイアの透過率は高くありませんが、ARコートによって

可視域では石英よりも高い透過率が得られます。当社は、 S9971/S7031シリーズなど電子冷却素子を内蔵したCCD には、標準の窓材としてサファイアを採用しています。

石英には合成石英と溶融石英がありますが、CCDの窓材としては金属不純物が少ない合成石英がよく使われます。石英は、ARコートなしでも可視域で約94%の透過率があります。石英は、200 nm以下の波長まで透過し、特に紫外域の検出時の窓材に適しています。しかし石英を冷却型CCDの窓材として使用する場合、接着部の樹脂の透湿性によるパッケージ内部の結露を考慮する必要がありました。当社では新技術の採用によって、石英窓の接着部に樹脂を用いないで気密封止を行うことが可能になりました。

当然ながら、窓材を使用しないタイプにおいて量子効率は最も高くなります。特に160 nm以下の真空紫外域では、透過する適当な窓材がないため、窓材を使用しない場合があります。

その他の窓材としては、石英に比べて安価な硼珪酸ガラスがあります。硼珪酸ガラスは、300 nm付近で急激に透過率が低下するため、主として可視域やそれ以上の長波長を検出対象とします。X線検出用としては、X線を透過して光を遮断するアルミニウムやベリリウムが窓材として使用される場合があります(ベリリウムは有毒です)。

#### [図2-6] 窓材の分光透過特性

KMPDB0110JA

# 2-4 感度不均一性

感度不均一性は、CCDの画素ごとの感度のバラツキを規定するもので、受光窓やプロセスのバラツキに起因して発生します。なお、感度不均一性に伴うノイズは、信号量に比例します。

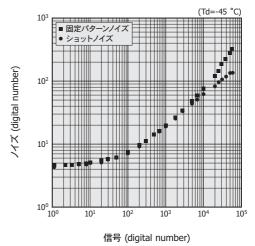

均一光を有効受光領域に入射して50 × 50画素程度 の測定領域を設定することによって、露光量に対応し た入力信号量とノイズの関係をプロットするフォトントラ ンスファー曲線 [図2-7]が得られます。感度不均一性 (PRNU: Photoresponse Nonuniformity)は、式 (2-4)で定義されます。

ここでのノイズは統計的な値であり、画素の信号の標準偏差です。信号は、有効受光領域における各画素の信号量の平均値です。信号量が少ない場合は、ショットノイズ(「2-9 ノイズ」参照)の影響を受けてしまいますが、十分な信号量の場合は、PRNUは一定の値になります。当社のデータシートでは、飽和電荷量の50%のときの測定値をPRNUとして示しています。標準的なFFT型CCDのPRNUは、約1% rmsまたは±3% typ. (peak to peak)です。

#### [図2-7] フォトントランスファー曲線 (S9974-1007)

KMPDB0210J

## 2-5 飽和電荷量

CCDの飽和電荷量は、ポテンシャルウェルによって転送できる信号電子数を示し、フルウェル (full well)とも呼ばれ、単位はe-で表されます。

CCDの飽和電荷量は、以下の4つによって決定されます。

- ・垂直シフトレジスタの飽和電荷量 (vertical full well)

- ・水平シフトレジスタの飽和電荷量 (horizontal full well)

- ・サミングウェルの飽和電荷量 (summing full well)

- ・ 出力部の飽和電荷量

2次元動作モードでは、各画素の信号電荷は分離して出力されるため、飽和電荷量は垂直シフトレジスタで決定されます。一方、水平シフトレジスタの飽和電荷量は、ラインビニングを可能にするため、垂直シフトレジスタの飽和電荷量より大きな値になるように設計されています。最終クロックゲートであるサミングゲートによって形成されるサミングウェルの飽和電荷量は、水平シフトレジスタの信号を加算するため(ピクセルビニング)、水平シフタの信号を加算するため(ピクセルビニング)、水平シフ

トレジスタの飽和電荷量よりも大きな値に設計されています。

出力信号の飽和電圧 (Vsat)は式 (2-5)で求められます。

$Vsat = FW \times Sv \cdots (2-5)$

FW:飽和電荷量 Sv:変換係数

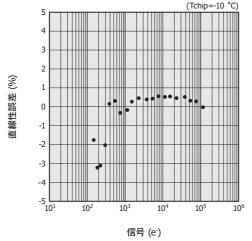

# 2-6 直線性

CCDの出力特性の直線性は、信号量によって理想的な直線である $\gamma$ =1からわずかにずれます。この原因は出力段に関係し、FDAを構成する逆バイアスされたPN接合の容量変化や、MOSFETのトランスコンダクタンスの変化によるものです。

直線性のズレを表す直線性誤差 (LR: Linearity Residual)は、式 (2-6)で定義されます。

LR =

$$(1 - \frac{Sm/Tm}{S/T}) \times 100 [\%] \dots (2-6)$$

Sm: 飽和電荷量の半分のときの信号量 Tm: 飽和電荷量の半分のときの露光時間

S :信号 T :露光時間

#### [図2-8] 直線性 (S9971-1007, 2次元動作, 代表例)

KMPDB0211J

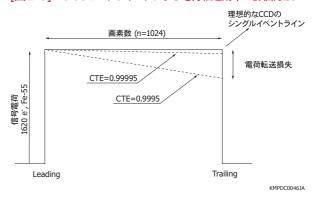

# 2-7 電荷転送効率

CCDは、理想的には電荷の転送過程における損失はありません。しかし実際は、材料に起因するトラップやプロセス工程で発生するトラップにより電荷の転送が完全にはいかず、ごくわずかの量は転送されずに残ってしまいます。

電荷転送効率 (CTE: Charge Transfer Efficiency) は、任意の1画素から隣接する画素へ転送される電荷の割合で規定されます (2相CCDでは、1画素分の信号電

荷を転送するのにゲート単位では2回の転送が必要ですが、これを1回として規定しています)。

X線を用いると、電気的な方法によらないでCCDの画素に理想的なポイント電荷を入力することができます。そのため、微小電荷の転送効率を測定するために有効な方法です。

水平スタッキング (stacking)は、水平方向に対して各ラインの信号を積み重ねることです。水平スタッキングを利用するとCCDの出力は、図2-9に示すようにX線のエネルギーに応じたシングルイベントライン (single event line)を描きます。理想的なCCDでは、CTE=1であるため、Leading (先頭)とTrailing (最後尾)で信号の高さは同じになります。実際のCTEは1より小さいため、Trailingでの信号電荷は電荷転送損失を生じ、Leadingでの信号電荷を1とすれば、電荷転送損失は式 (2-7)で表されます。

電荷転送損失 = n × CTI ······· (2-7)

n: 画素数 CTI (Charge Transfer Inefficiency: 非転送効率) = 1 - CTE

当社の標準的なCCDは、CTE=0.99999 typ.です。

#### [図2-9] Fe-55のスタッキングによる電荷転送効率の評価方法

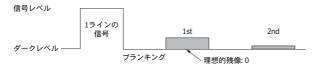

インターライン型のCCDでは受光部のフォトダイオードからシフトレジスタへの信号の転送が不完全であるため、数%程度の残像が存在することがあります。一方でFFT型CCDのようにシフトレジスタ自身が受光する場合では、トラップ(「3-9 放射線損傷」参照)による信号電荷の捕獲と放出による残像が生じます。この残像は結果としてはCTEの劣化として観察されます。ここではラインビニングの場合を例にCTEによる残像について簡単に示します。

ラインビニングでは、水平シフトレジスタの数の信号数をもつ1ラインの信号が得られます。CTEが1 (理想的)の場合には、1ラインの信号の後の読み出しにおいて信号電荷はダークレベルと同じになりますが、CTEが1未満の場合には転送数により表2-1に示すような信号電荷が読み残されることになります。

#### [図2-10] ラインビニング時のCCDの残像

KMPDC00473

[表2-1] ラインビニング時の電荷転送効率と残像の割合

| CTE     | S9971-0906 | S9971-0907 |

|---------|------------|------------|

| 0.99995 | 0.0032     | 0.0064     |

| 0.99999 | 0.00064    | 0.00128    |

| 0.99995 | 0.00032    | 0.00064    |

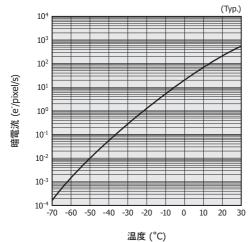

## 2-8 暗電流

暗電流は、光入力のない状態における電流出力です。 単位としては、一般にA(アンペア)、A/cm²、V(ボルト) が用いられますが、計測用CCDでは単位時間に1画素当 たりで発生する電子数を示すe<sup>-</sup>/pixel/sやe<sup>-</sup>/pixel/hが 一般的に用いられます。温度が5~7°C上昇すると、暗 電流はほぼ倍になります。

CCDで暗電流が発生する主な原因は、以下の3点です。

- ① 空乏化していない領域での熱励起とその拡散

- ② 空乏層内での熱励起

- ③ 表面準位による熱励起

この中では③が最も支配的です。

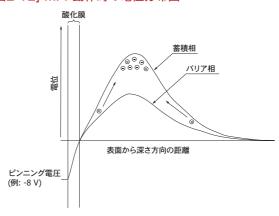

MPP (Multi-Pinned Phase)動作は、暗電流を下げるための動作で、反転動作とも呼ばれます。MPP動作は、CCDの電極を構成するMOS構造のすべてのゲート下を反転状態にすることにより実現できます。

MPP動作では、③の影響を抑制でき暗電流を大幅に 低減できます。

[図2-11] 暗電流-温度 (S9970/S9971シリーズ)

KMPDB0152JB

2相CCDでは、バリア相と信号電荷を蓄積する蓄積相にイオン注入などにより電位差が設けられています。したがって、すべてのゲートが同じ電圧になった場合でも、2相CCDは電荷を蓄積するためのポテンシャルウェルをもつことができます。CCDのすべての相が反転状態になるようにバイアスすることによって、MPP動作を実現できます。

暗電流を低減する必要がある場合には、このMPP動作とCCDの冷却が非常に効果的です。

#### [図2-12] MPP動作時の電位分布図

KMPDB0055JB

図2-12で示すように、MPP動作時には蓄積相・バリア相がともに反転状態にピンニング(pinning)されます。ピンニングされた状態では、CCD表面がチャンネル分離領域から供給された正孔によって反転され、それ以上の電圧を負側に印加しても酸化膜界面の電位は基板と同じ電位に固定されます。

酸化膜界面が正孔によって反転された状態においては、熱励起電子の発生が極端に抑制されるため、暗電流の少ない状態が実現できます。

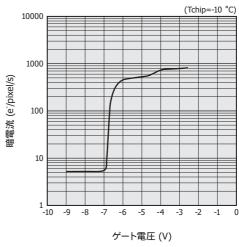

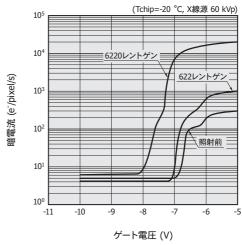

#### [図2-13] 暗電流-ゲート電圧 (S9974-1007, 代表例)

KMPDB02123B

MPP動作においては、ピンニング電圧 (ピンニングされるときの電圧)を正確に印加することによって暗電流

を大幅に低減することができます。ピンニング電圧に満たないと、正孔による反転層の形成が不十分なため、暗電流が最小まで下がりません。一方、ピンニング電圧を超えて大きく負の値をとると、余分なクロック振幅が必要となるばかりでなく、スプリアスチャージ(「2-14 スプリアスチャージ」参照)という過剰電荷によって暗電流が増加することがあります。データシートに記載されたゲート電圧の付近で可変させて電圧を調整することによって、暗電流を最小にすることができます。

## 2-9 ノイズ

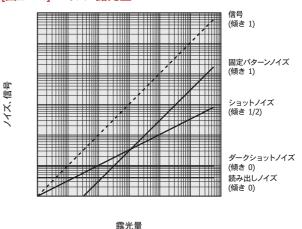

CCDのノイズは、以下の4種類に分類されます。

#### (1) 固定パターンノイズ (Nf: fixed pattern noise)

CCDの画素間の感度のバラツキによるノイズです(画素間の感度のバラツキは、開口面積や膜厚のバラツキによって発生します)。固定パターンノイズは、信号量が大きい場合、露光量(信号電子量)に比例します。なお、1 画素のノイズについて考える場合は、Nf=0になります。

#### (2) ショットノイズ (Ns: shot noise)

CCDに入射するフォトン数の統計的な変化により発生するノイズです。ショットノイズは、ポアソン統計に従い式(2-8)で表されます。

$$Ns = \sqrt{S}$$

..... (2-8)

S: 信号電子数 [e<sup>-</sup>]

たとえば、フォトンの入射によりCCD内で信号電子量が 10000 e-発生する場合には、ショットノイズは100 e- rms です。

#### (3) ダークショットノイズ (Nd: dark shot noise)

ダークショットノイズは、暗電流によって発生するノイズで、暗電子数の平方根に比例します。ダークショットノイズを低減するためには、暗電流そのものを低減する必要があります。なお、画素間の暗電流のバラツキは、感度のバラツキよりも大きくなっています。

#### (4) 読み出しノイズ (Nread: readout noise)

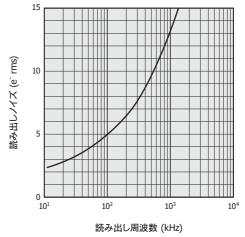

CCDの出力部のアンプを構成するMOSFETに起因する熱雑音と読み出し回路に起因する電気的なノイズで、最終的にCCDの検出限界を制限します。このノイズは、CCDの出力方式によって決まり、露光量の影響は受けません。また読み出しノイズは、周波数依存性をもちます[図2-18]。

トータルノイズ (Nt)は、式 (2-9)で表されます。

$$Nt = \sqrt{Nf^2 + Ns^2 + Nd^2 + Nr^2}$$

..... (2-9)

図2-14は、これらの4種類のノイズと露光量の関係を示しています。CCDの検出限界は、ダークショットノイズと読み出しノイズによって決まります。暗電流を下げてダークショットノイズを読み出しノイズ以下に下げることで、CCDの検出限界を読み出しノイズまで下げることができます。

S/Nは、露光量が大きい場合では主として固定パターンノイズによって決まり、露光量が小さい場合はショットノイズによって決まります。

#### [図2-14] ノイズ-露光量

KMPDB0057JB

# 2 - 10 ダイナミックレンジ

ダイナミックレンジは、一般に検出器の測定可能範囲 を規定するもので、最大レベルと最小レベル (検出限界)の比で定義されます。

CCDのダイナミックレンジは、飽和電荷量を読み出しノイズで割った値です。

ダイナミックレンジは、式 (2-11)でも表されます。

ダイナミックレンジ =

$$20 \times log \left( \frac{飽和電荷量}{ 読み出しノイズ} \right) [dB] \cdots (2-11)$$

動作温度や蓄積時間などの動作条件によってダイナミックレンジは変わってきます。室温付近ではダークショットノイズが検出限界を決定しますが、ダークショットノイズが無視できるような動作条件(十分に冷却した状態)では、読み出しノイズによってダイナミックレンジが決まります。

2次元動作では、垂直シフトレジスタが転送できる電荷量が飽和電荷量になります。ラインビニングでは、水平シフトレジスタの転送できる電荷量が飽和電荷量になります。

#### [表2-2] CCDの仕様例

| 項目                                  | S9736シリーズ   | S7170-0909 |  |  |  |

|-------------------------------------|-------------|------------|--|--|--|

| タイプ                                 | 表面入射型       | 裏面入射型      |  |  |  |

| 画素数                                 | 512 × 512   |            |  |  |  |

| 画素サイズ [μm]                          | 24          |            |  |  |  |

| 飽和電荷量 (垂直) [ke⁻]                    | 300         | 320        |  |  |  |

| 変換係数 [μV/e⁻]                        | 3.5         | 2.2        |  |  |  |

| 読み出しノイズ [e⁻ rms]                    | 4           | 8          |  |  |  |

| ダイナミックレンジ                           | 75000 40000 |            |  |  |  |

| 暗電流 (0°C) [e <sup>-</sup> /pixel/s] | 1           | 0          |  |  |  |

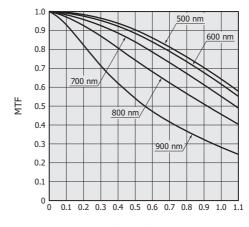

## 2 - 11 解像度

イメージセンサが、ある画像内の空間的な周波数のコントラストを再現する性能は空間解像力と呼ばれ、サイン波に対するMTF (Modulation Transfer Function)で定量化されます。CCDの画素は分離しているため、離散サンプリング定理によりナイキスト (Nyquist)限界によって決定される限界解像度があります。たとえば、入力が白黒のパターンの場合に、パターンが細かくなるに従って、信号の白レベルと黒レベルの差が小さくなって、最終的には解像できなくなります。CCDの理想的なMTFは式(2-12)で表されます。

MTF = sinc

$$\{(\pi \times f)/(2 \times fn)\}$$

...... (2-12)

f:画像の空間周波数 fn:空間ナイキスト周波数

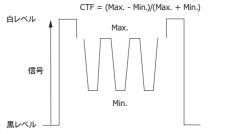

光学的なサイン波を実現することは難しいため、一般には矩形波のパターンをもったテストチャートが代用されます。この場合の空間周波数特性は、コントラスト伝達関数 (CTF: Contrast Transfer Function)と呼ばれ、MTFとは異なります(CTFはフーリエ変換によりMTFに変換できます)。

実際のCCDの解像度は、Si内で電荷が収集されるときに起きる拡散によって決まります。入射フォトンが空乏層内で吸収されることによって、発生した電子は広がることなくその画素に収集され、解像度の劣化は起きません。解像度は入射フォトンが吸収される深さによっても変わり、入射フォトンの波長が長いほど深く吸収されて解像度は劣化します。

#### [図2-15] MTF-空間周波数 (S9970/S9971シリーズ, 計算値)

空間周波数 (f/fn)

KMPDB0206JA

#### [図2-16] CTFの計算方法

KMPDC0048JA

# 2 - 12 点像分布関数 (point spread function)

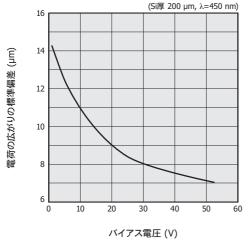

空乏層内における電荷の広がりの標準偏差 (σD)は、式 (2-13)で定義されます。σDは、Siの空乏層厚さと絶対温度の平方根に比例し、裏面に印加するバイアス電圧の平方根に逆比例します。

$$OD = \sqrt{\frac{2 \times X dep^2 \times k T}{Vbb \times q}} \cdots (2-13)$$

Xdep: 空乏層の厚さ k : ボルツマン定数 T : 絶対温度

Vbb: 裏面に印加するバイアス電圧

q: 1電子当たりの電荷量

[図2-17] 電荷の広がりの標準偏差ーバイアス電圧

KMPDB0281JB

# 2-13 ノイズの周波数特性

暗電流やスプリアスチャージ(spurious charge)が十分に小さい状態では、読み出しノイズがCCDの最終的なノイズ電子数を決定します。読み出しノイズは、読み出し部のFDAを構成するMOSFETの熱雑音によって決まります。MOSFETの熱雑音には、ホワイトノイズと1/fノイズがあり、低ノイズを実現するためにはホワイトノイズと1/fノイズの両方を低減する必要があります。ホワイトノイズは、MOSFETの相互コンダクタンス(gm)を増加させることによって低減できます。計測用CCDに内蔵されているMOSFETの1/fノイズのコーナ周波数は、数kHz程度と低くなっています。

また、MOSFETの熱雑音は、バイアス条件に大きく影響を受けます。当社のデータシートに掲載されている読み出しノイズを実現するためには、推奨動作条件に従ってバイアスすることが必要です。しかし、上記のバイアス条件に設定した場合でも、CCDの読み出しノイズは、信号処理回路によって大きく影響されます。CCDの信号処理には一般にCDS回路が使われ、CDS回路とその前段に設けたLPF(Low-Pass Filter)の伝達関数を最適化することが、CCDの読み出しノイズの低減につながります。CCDの読み出し周波数に対して1/fノイズのコーナ周波数の影響を低減できれば、信号処理回路を含めたCCDシステムの出力ノイズは、ホワイトノイズとノイズ帯域幅で決まることになります。

以上によりCCDの読み出しノイズは、読み出し周波数に依存し、計測レベルで必要とされる数e<sup>-</sup>rmsレベルの読み出しノイズが達成できるのは、読み出し周波数が低い場合(100 kHz以下)になります。読み出し周波数が高くなると、読み出しノイズは急激に増加します。

#### [図2-18] 読み出しノイズ-読み出し周波数 (S9737-01, 代表例)

KMPDB0207JA

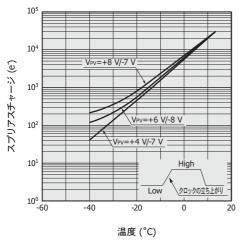

# 2 - 14 スプリアスチャージ

スプリアスチャージは、MPP動作時などにクロックパルスによって発生する電荷で、入射光による信号以外の電荷です。MPP動作時には、垂直クロックパルスがLowレベルにセットされ、この期間は各画素のゲート下は反転状態になっています。この状態では、チャンネルストップ領域から正孔がゲート下に移動して、その領域の表面電位は基板の電位にピン(pin)されています。このときに、正孔のうちのいくらかは酸化膜界面に沿ってトラップされ、クロックパルスがHighレベルとなるときに各画素のゲート相は非反転状態になります。トラップされた正孔は、放出された後に高いエネルギーをもち、これによりスプリアスチャージが発生しポテンシャルウェルに集められます。CCDの出力は、信号と暗電流とスプリアスチャージが加算された値となります。

スプリアスチャージは、クロックパルスの立ち上がりを遅くしたり、クロックパルスのHighレベルとLowレベルの電位差を小さくすることによって改善できます。CCDが十分低い温度まで冷却され、読み出しノイズレベルに近い信号量になる場合には、スプリアスチャージを考慮したクロッキングが重要になります。

#### [図2-19] スプリアスチャージ-温度 (代表例)

#### KMPDB02083

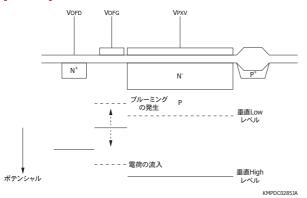

# 2 - 15 アンチブルーミング

受光面に強い光が入り信号電荷が特定量を超えた場合に、余剰電荷が隣接した画素や転送領域にあふれ出る現象がブルーミング(オーバーフロー)です。ドレインを設けて余剰電荷を捨てることによりブルーミングを防止することをアンチブルーミングといいます。

CCDのアンチブルーミング構造には大きく分けて横型と縦型があり、当社のCCDでは横型を採用しています。 横型は、画素もしくは電荷転送路の脇にドレインを設けた構造で、表面入射型CCDでは開口率が小さくなる欠点があります。一方、裏面入射型CCDでは、この欠点を回避することができます。縦型は、余剰電荷を基板内部に捨てる構造で、開口率は小さくなりませんが長波長の感度が低下する欠点があります。

なお、オーバーフロードレイン電圧 (Vofd)とオーバーフローゲート電圧 (Vofd)によりアンチブルーミング機能を制御する場合、印加電圧により飽和電荷量が低下することがあるため注意が必要です。

#### [図2-20] アンチブルーミングの概念図

#### [図2-21] アンチブルーミング構造 (横型)とポテンシャル

#### [図2-22] 撮像例

#### (a) アンチブルーミングなし (b) アンチブルーミングあり

#### ◆ CCDリニアイメージセンサのアンチブルーミング機能

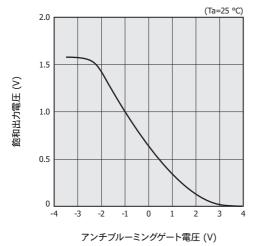

CCDリニアイメージセンサでは、ストレージゲートの近くにアンチブルーミングドレインとアンチブルーミングゲートが形成されています。アンチブルーミングドレインとアンチブルーミングゲートに適切な電圧を印加することでアンチブルーミング機能を使うことができます。アンチブルーミングゲート電圧によって、飽和出力電圧を制御します。また、アンチブルーミングゲート電圧を高くすることで、フォトダイオードで発生した信号電荷をすべてアンチブルーミングドレインに掃き出し、出力をゼロにすることも可能です。この機能を使って、後述の電子シャッタを機能させることができます。

#### [図2-23] 飽和出力電圧ーアンチブルーミングゲート電圧 (代表例)

KMPDB0282JA

# 2-16 電子シャッタ

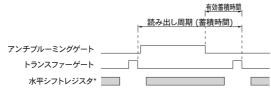

CCDリニアイメージセンサの蓄積時間は、通常はトランスファーゲートの2つのクロックパルスの間隔になります。電子シャッタ機能を使うことで、トランスファーゲートのクロックの間隔よりも短い有効蓄積時間に設定することが可能です。アンチブルーミングゲートの電圧を高くすると、フォトダイオードで発生した信号電荷はすべてアンチブルーミングドレインに捨てられます。トランスファーゲートのクロックの間にアンチブルーミングゲートの電圧を高くする期間と低くする期間を設けることで、通常の蓄積時間よりも短い有効蓄積時間を実現できます。また、蓄積時間の開始タイミングを外部トリガパルスと同期させることができます。

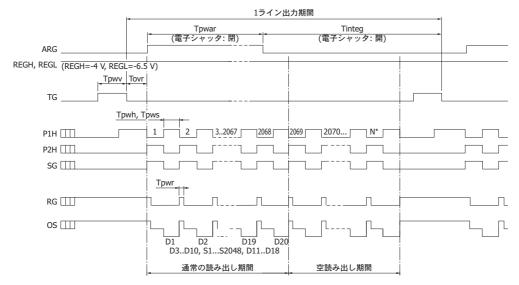

# [図2-24] CCDリニアイメージセンサのタイミングチャート (電子シャッタ機能)

\* 読み出しを行っている期間を表す。

KMPDC0287JA

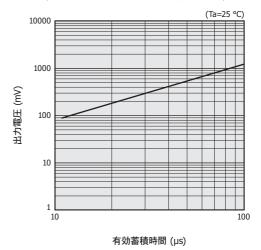

#### [図2-25] 出力電圧一有効蓄積時間 (CCDリニアイメージセンサ, 代表例)

KMPDB0283JA

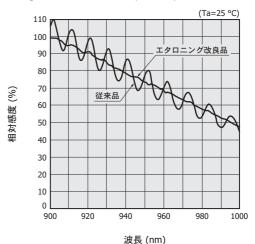

### 2 - 17 エタロニング

エタロニングは、入射した光がCCDの表面と裏面で反射と減衰を繰り返す間に、干渉により感度に強弱が現れる現象です。一般にエタロニングとは2面の高反射フィルタを向き合わせて配置した光学素子のことを指しますが、CCD内部でも入射した光が不完全な反射・透過・吸収を繰り返し、エタロニングのような振る舞いをするため、このように呼ばれます。裏面入射型CCDの場合、Siの厚さと吸収長との関係から、入射光が長波長の場合、エタロニングが発生します[図2-26]。当社では、独自に開発した技術でエタロニングを低減した裏面入射型CCDを製品化しました。なお、エタロニングは裏面入射型CCDに特有の現象であり、表面入射型CCDではみられません。

#### [図2-26] エタロニング特性 (代表例)

KMPDB0284JE

# 2 - 18 コスメティックス

コスメティックスは、CCDの欠陥 (汚れ、傷)のレベルを示すものです。汚れや傷は、暗状態で明るく見える白キズ (white spot)と入射光のある状態で暗く見える黒キズ (black spot)の2種類に分類できます。

白キズの発生する原因としては、材料の格子欠陥、材料に含まれる金属不純物、機械的損傷やプロセス中の埃に起因するパターン不良などがあります。黒キズは、プロセス中のCCD表面への埃や表面の絶縁膜の部分的欠陥による反射の違い、素子の表面や窓材における埃などの汚れによるものです。白キズ・黒キズをゼロに保つことは難しく、面積が大きく画素サイズが小さいCCDほどキズの影響は顕著になります。

当社は、白キズと黒キズの仕様を定めて、すべての CCDに対して、その量を検査しています。

コスメティックスの定義を以下に示します。メーカーに よって定義に差がありますので、比較する場合には注意 が必要です。

#### (1) ポイント欠陥 (point defect)

#### 白キズ

冷却温度 0°Cで1秒間蓄積したときに、飽和電荷量の3%を超える暗電流が発生する画素を白キズとして定義しています。

#### ■ 黒キズ

飽和電荷量の50~90%になるように、CCDに均一光を入射します。このときの各画素の出力の平均値を算出し、平均値の50%以下の出力の画素を黒キズとします。 当社は、通常、飽和電荷量の50%になるような均一光で検査をしています。

#### (2) クラスタ欠陥 (cluster defect)

連続した画素欠陥で2~9個の固まりをクラスタ欠陥と呼び、ポイント欠陥と区別します。クラスタ欠陥は、縦方向にみられる場合が多いですが、裏面入射型CCDやFOS (Fiber Optic plate with Scintillator)がカップリングされた表面入射型CCDの黒キズに起因するクラスタ欠陥は、2次元的な固まりとしてみられます。

#### (3) コラム欠陥 (column defect)

連続した画素欠陥で10個以上の固まり(クラスタ欠陥よりも大きいもの)をコラム欠陥と呼び、クラスタ欠陥とは区別します。コラム欠陥も縦方向にみられる場合が多いですが、裏面入射型CCDやFOSがカップリングされた表面入射型CCDの黒キズに起因するコラム欠陥は、クラスタ欠陥と同様に2次元的な固まりとしてみられます。

S9970/S9971シリーズのように受光面積の小さな表面入射型CCDは、ポイント欠陥・クラスタ欠陥・コラム欠陥はゼロになっています。FOP (Fiber Optic Plate)やFOSをカップリングしたCCDでは、CCD以外の要因で欠陥が発生するため、欠陥の形状や数はCCDのみの場合とは異なります。

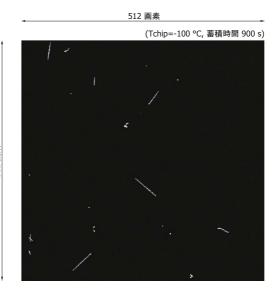

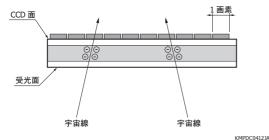

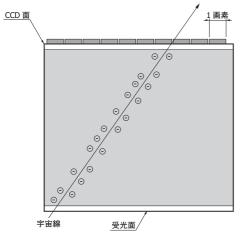

# 2 - 19 宇宙線によるCCDへの影響

CCDに宇宙線が入射した場合、図2-27のように宇宙線が検出される場合があります。宇宙線は、ある程度の割合で地表に降り注いでいます。主なものはµ粒子(~数GeV)で、CCDのSi内部で飛跡に沿って信号電荷を発生させます[図2-28]。標準タイプ裏面入射型CCDの場合はSiが薄いため、宇宙線による偽信号が現れるのは多くても数画素程度ですが、完全空乏化タイプ裏面入射型CCDでは、多数の画素で偽信号が現れる場合があります。

宇宙線が検出される頻度は、センサ構造や環境によって異なりますが、おおよその目安として150個/(cm²・h)程度です。なお、地表から離れるほど、宇宙線の量は増えることが知られています。

宇宙線によって一時的に偽信号が発生する場合は、 複数回の画像を取得して平均化したり、蓄積時間を短く することによって、その影響を低減できます。

宇宙線は、Si原子との相互作用により格子欠陥を発生させる場合があり、白キズや電荷トラップの原因となります。あらかじめ白キズに対する補正機能を装置に加えることを推奨します。

[図2-27] 完全空乏化タイプ裏面入射型CCDにおける 宇宙線による擬似信号発生画像例

#### [図2-28] 宇宙線が入射したCCD (裏面入射型)の断面図

#### (a) 標準タイプ

#### KMPD

#### (b) 完全空乏化タイプ

KMPDC0413JA

# 3. 使い方

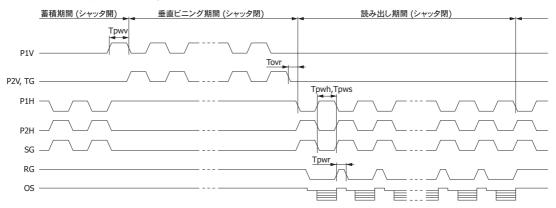

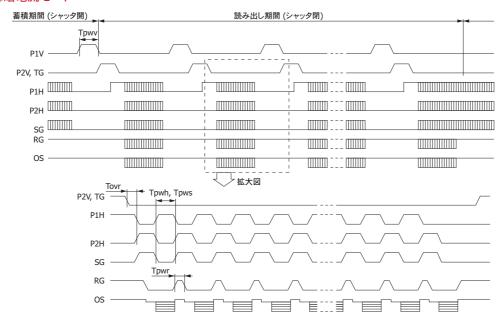

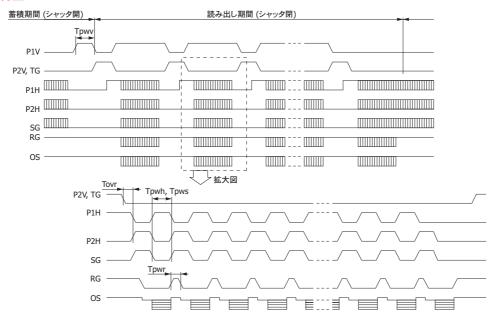

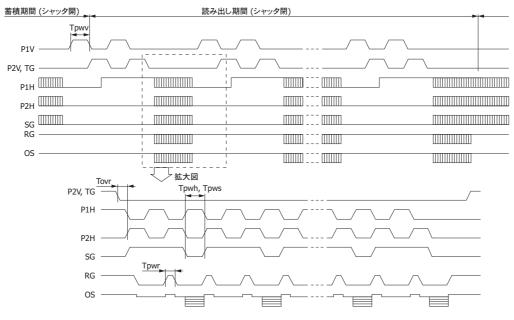

## 3-1 タイミング

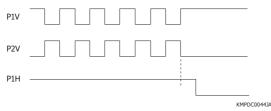

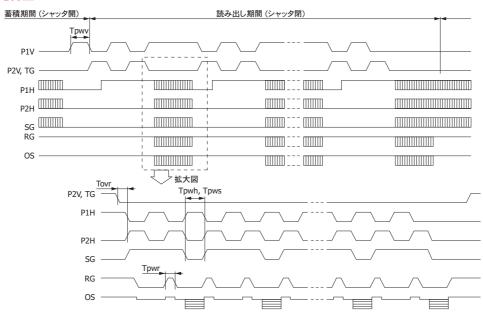

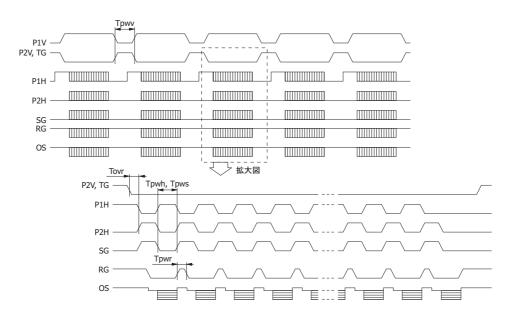

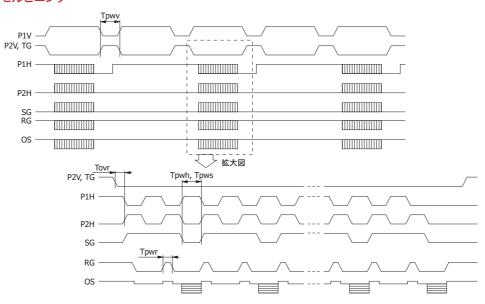

CCDを動作させるためには、垂直シフトレジスタ用2相クロックパルス (P1V, P2V)、トランスファーゲートパルス (TG)、水平シフトレジスタ用2相クロックパルス (P1H, P2H)、サミングゲートパルス (SG)、リセットパルス (RG)の7つの信号が必要になります。TGは、最終のP2V電極を分割したもので、P2Vと同じタイミングで別端子としてクロックパルスを入れることを推奨しますが、P2V端子と短絡させることによっても動作します。CCDの動作に必要なパルスのタイミングチャートについてはデータシートを参照してください。

FFT型CCDには、ラインビニング・2次元動作・ピクセルビニング・TDI動作という4つの動作モードがあります。これらの動作モードは、各動作のタイミングを調整することで、簡単に選択することができます。

#### (1) ラインビニング

最初に、ビニングしたいビット数だけ垂直方向を転送します。これによって、対応する水平レジスタに電荷が加算されます。その後、水平方向をすべて転送します。サミングゲートパルスは、水平シフトレジスタ用クロックパルス(P2H)とまったく同じパルスにします。

#### (2) 2次元動作 (エリアスキャン)

垂直方向に1ビット転送するごとに、水平方向をすべて転送します。垂直方向がすべて転送し終わったとき、フレームの転送が終了することになります。このとき、サミングゲートパルスは、水平シフトレジスタ用クロックパルス(P2H)とまったく同じパルスにします。

#### (3) ピクセルビニング

最初に、垂直方向は1ビットの転送をします。その後、水平方向をすべて転送しますが、このときサミングゲートパルスをサミングするビット数だけパルスを止めると、サミングウェルに電荷が加算されます。

注) ラインビニングとピクセルビニングは、同時に動作させることもできます。

#### (4) TDI動作

「1-11 TDI-CCD」で説明したように、TDI動作によって移動する物体の画像化が可能になります。そのためには、被写体の受光面上での移動速度とCCDの垂直転送クロックパルスを同期させる必要があります。

#### [図3-1] ラインビニングのタイミングチャート

KMPDC0050JB

| 項目                     |           |                  | 記号   | Min. | Тур. | Max. | 単位 |

|------------------------|-----------|------------------|------|------|------|------|----|

|                        |           | S703*-0906       |      | 1.5  | 2    | -    |    |

| P1V, P2V, TG*1         | パルス幅      | S703*-0907/-1006 | Tpwv | 3    | 4    | -    | μs |

| FTV, FZV, TG           |           | S703*-1007       |      | 6    | 8    | -    |    |

|                        | 上昇/下降     | 上昇/下降時間          |      | 10   | -    | -    | ns |

|                        | パルス幅      | パルス幅             |      | 500  | 2000 | -    | ns |

| P1H, P2H* <sup>1</sup> | 上昇/下降     | 上昇/下降時間          |      | 10   | -    | -    | ns |

|                        | デューティ     | デューティ比           |      | -    | 50   | -    | %  |

|                        | パルス幅      | パルス幅             |      | 500  | 2000 | -    | ns |

| SG                     | 上昇/下降     | 上昇/下降時間          |      | 10   | -    | -    | ns |

|                        | デューティ     | デューティ比           |      | -    | 50   | -    | %  |

| RG                     | パルス幅      | パルス幅             |      | 100  | -    | -    | ns |

|                        | 上昇/下降     | 上昇/下降時間          |      | 5    | -    | -    | ns |

| TG-P1H                 | オーバーラップ時間 |                  | Tovr | 3    | -    | -    | μs |

<sup>\*1:</sup> 最大パルス振幅の50%のところに対称クロックパルスをオーバーラップさせてください。

#### [図3-2] 2次元動作のタイミングチャート

#### (a) 低暗電流モード

KMPDC0049JB

#### (b) 大飽和電荷量モード

KMPDC00145JA

| 項目           |                    | センサ           | 記号         | Min. | Тур. | Max. | 単位 |

|--------------|--------------------|---------------|------------|------|------|------|----|

| P1V, P2V, TG | パルス幅* <sup>2</sup> | S7171-0909-01 | Tpwv       | 6    | 8    | -    | μs |

| FIV, FZV, IG | 上昇/下降時間            |               | Tprv, Tpfv | 200  | -    | -    | ns |

|              | パルス幅* <sup>2</sup> |               | Tpwh       | 500  | 2000 | -    | ns |

| P1H, P2H     | 上昇/下降時間            |               | Tprh, Tpfh | 10   | -    | -    | ns |

|              | デューティ比             |               | -          | 40   | 50   | 60   | %  |

|              | パルス幅               | ー 全シリーズ       | Tpws       | 500  | 2000 | -    | ns |

| SG           | 上昇/下降時間            |               | Tprs, Tpfs | 10   | -    | -    | ns |

|              | デューティ比             |               | -          | 40   | 50   | 60   | %  |

| RG           | パルス幅               |               | Tpwr       | 100  | -    | -    | ns |

|              | 上昇/下降時間            |               | Tprr, Tpfr | 5    | -    | -    | ns |

| TG-P1H       | オーバーラップ時間          |               | Tovr       | 3    | -    | -    | μs |

<sup>\*2:</sup> 最大パルス振幅の50%のところに対称クロックパルスをオーバーラップさせてください。

#### [図3-3] ピクセルビニング(2 x 2)のタイミングチャート

#### (a) 低暗電流モード

KMPDC0051JB

#### (b) 大飽和電荷量モード

KMPDC0146JA

| 項目                     |           |                  | 記号         | Min. | Тур. | Max. | 単位 |

|------------------------|-----------|------------------|------------|------|------|------|----|

| P1V, P2V, TG*3         |           | S703*-0906       |            | 1.5  | 2    | -    |    |

|                        | パルス幅      | S703*-0907/-1006 | Tpwv       | 3    | 4    | -    | μs |

|                        |           | S703*-1007       |            | 6    | 8    | -    |    |

|                        | 上昇/下降時間   |                  | Tprv, Tpfv | 10   | -    | -    | ns |

| P1H, P2H* <sup>3</sup> | パルス幅      |                  | Tpwh       | 500  | 2000 | -    | ns |

|                        | 上昇/下降時間   |                  | Tprh, Tpfh | 10   | -    | -    | ns |

|                        | デューティ比    |                  | -          | -    | 50   | -    | %  |

|                        | パルス幅      |                  | Tpws       | 500  | 2000 | -    | ns |

| SG                     | 上昇/下降時間   |                  | Tprs, Tpfs | 10   | -    | -    | ns |

|                        | デューティ比    |                  | -          | -    | 50   | -    | %  |

| RG                     | パルス幅      |                  | Tpwr       | 100  | -    | -    | ns |

|                        | 上昇/下降     | 上昇/下降時間          |            | 5    | -    | -    | ns |

| TG-P1H                 | オーバーラップ時間 |                  | Tovr       | 3    | -    | -    | μs |

<sup>\*3:</sup> 最大パルス振幅の50%のところに対称クロックパルスをオーバーラップさせてください。

#### [図3-4] TDI動作のタイミングチャート

#### (a) $1 \times 1$

KMPDC0147JA

注) 低暗電流モードでのタイミングチャートは、図3-2 (a)のP1V、P2V、TGを参考にしてください。

#### (b) 2 × 2、ピクセルビニング

KMPDC0148JA

注) 低暗電流モードでのタイミングチャートは、図3-3 (a)のP1V、P2V、TGを参考にしてください。

| 項目                                     | センサ       | 記号       | Min.       | Тур. | Max. | 単位 |    |

|----------------------------------------|-----------|----------|------------|------|------|----|----|

| P1AV, P1BV                             | パルス幅      |          | tpwv       | 30   | -    | -  | μs |

| P2AV, P2BV, TG*4 *5                    | 上昇/下降時間   |          | tprv, tpfv | 200  | -    | -  | ns |

| P1AH, P1BH<br>P2AH, P2BH* <sup>5</sup> | パルス幅      |          | tpwh       | 125  | -    | -  | ns |

|                                        | 上昇/下降時間   | S7199-01 | tprh, tpfh | 10   | -    | -  | ns |

|                                        | デューティ比    |          | -          | -    | 50   | -  | %  |

|                                        | パルス幅      |          | tpws       | 125  | -    | -  | ns |

| SG                                     | 上昇/下降時間   |          | tprs, tpfs | 10   | -    | -  | ns |

|                                        | デューティ比    |          | -          | -    | 50   | -  | %  |

| RG                                     | パルス幅      |          | tpwr       | 10   | -    | -  | ns |

|                                        | 上昇/下降時間   |          | tprr, tpfr | 5    | -    | -  | ns |

| TG-P1AH, P1BH                          | オーバーラップ時間 |          | tovr       | 10   | -    | -  | μs |

<sup>\*4:</sup> TGにP2AVと同じパルスを入力してください。

<sup>\*5:</sup> 最大パルス振幅の50%のところに対称クロックパルスをオーバーラップさせてください。

# 3 - 2 クロックパルス、DCバイアスの調整

CCDの性能を最大限に利用するためには、クロックパルスやDCバイアスを調整する必要があります。

#### (1) 転送クロックパルス

垂直シフトレジスタのクロック電圧のLowレベルは、CCDの暗電流に影響し、MPP動作になるピンニング電圧より高い電圧に設定した場合には、期待したほどには暗電流が下がらなくなります。ピンニング電圧は、製造時のバラツキなどにより個々のCCDで異なるため、理想的には製品ごとに調整する必要があります。

垂直のクロック電圧のLowレベルを決定した後に、 Highレベルを調整します。飽和電荷量を確保するためには、クロックパルスの振幅をある程度大きくする必要があります。ただしクロックパルスの振幅が大きすぎると、スプリアスチャージが大きくなってしまい、読み出し時間中の暗電流(Nb)が大きくなり、結果として出力信号全体にわたるオフセットの形で現れます。通常スプリアスチャージは、室温付近では暗電流とは区別できませんが、CCDを冷却した状態においては問題になることがあります。したがって垂直クロックパルスの振幅は、他の特性に対して問題ない範囲で最小になるように調整する必要があります。

#### (2) リセットクロックパルス

リセットクロックパルスは、リセットゲート(RG)に加えるクロックパルスで、FD(Floating Diffusion)に流れ込んだ信号電荷を定期的にリファレンス電圧(VRD)にリセットします。クロックパルスのLowレベル・Highレベルの調整によって、出力部の飽和電荷量が変化します。出力部の飽和電荷量は、適切に調整された状態では、CCDの飽和電荷量よりは十分に大きくなります。リセットクロックパルスのLowレベルの電圧が高くなると、リセットスイッチがオフになった状態での電位が十分に下がっていないためFDに蓄積できる電荷量が減少し、転送電荷のすべてを電圧に変換する前にオーバーフローしてしまうことがあります。このため、リセットクロックパルスのLowレベルは、出力部の飽和電荷量に影響しないように十分に低い電圧に設定することが必要です。

リセットクロックパルスのパルス幅は、10 ns~100 ns 程度に設定してください (100 nsよりも長くても問題は 生じません)。

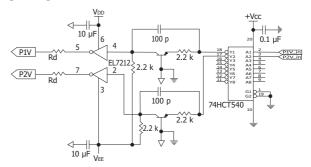

#### (3) 転送クロックパルス生成回路

転送クロックパルス生成回路の例を図3-5に示します。 前述の通りCCDを動作させるためには、HighレベルとLow レベルの電圧振幅をもつクロックパルスが必要です。この クロックパルスは数百pF~数nFの入力容量をもつ垂直 シフトレジスタや水平シフトレジスタを高速で動作させなければなりません。このため、一般にCCDを駆動する場合は、容量性負荷を高速で駆動できるMOSドライバが使用されます。

通常、タイミング信号発生回路には、TTLもしくは CMOSロジックレベルのICを使用します。これらの動作 電圧は、+3.3 Vもしくは+5.0 Vであるため、MOSドライバ にはレベル変換回路を接続する必要があります。

2相CCDの場合では、垂直シフトレジスタや水平シフトレジスタを駆動するクロックパルスはオーバーラップが必要です(「1-2 電荷転送動作」参照)。このため、MOSドライバICとCCDの間には適当な値の抵抗 Rd(ダンピング抵抗:数 $\Omega$ ~数十 $\Omega$ )を挿入し、クロックパルスの上昇時間と下降時間を調整します。

デジタル系回路からのCCDへのノイズ混入をできるだけ減らすため、アナログ系グランドとデジタル系グランドは転送クロックパルス生成回路で同電位とすることを推奨します。

#### [図3-5] 転送クロックパルス生成回路の例

Vod: クロックパルスHighレベル電圧 Vee: クロックパルスLowレベル電圧 Rd: ダンピング抵抗 (数 $\Omega$ ~数十 $\Omega$ )

KMPDC0052JE

#### [図3-6] CCD出力部の電位

#### (4) DCバイアス

#### ■ ODに加えるバイアス (Vob)

Vopは、出力トランジスタに加えるバイアスです。1段

ソースフォロワ出力形式のアンプでは、Vonとして約20 Vを印加してください。ソースフォロワ回路においてMOSFETのソースに接続した20 kΩ程度の負荷抵抗では、ソースのDCレベルは15 V程度になっています。したがって、ODに加える電圧によりMOSFETのソースドレイン間には数V程度の電圧が加わりますが、この電圧が十分に高くないと次の現象が発生します。

- ① ソースフォロワ回路の電圧ゲイン (Av)が低くなる。

- ② MOSFETが飽和領域で動作しない。

これらの現象によって、CCDの変換係数(単位:  $\mu V/e^-$ )の低下や読み出しノイズの増加、直線性の悪化など、性能に悪影響があります。

2段ソースフォロワ出力形式などの多段のアンプでは、 Vonは約+15 Vで1段の場合に比べて低くします。なお、2 段ソースフォロワ出力形式の場合も、1段と同様に①②の 現象が発生します。

#### ■ RDに加えるバイアス (VRD)

VRDはリセットドレインに加えるバイアスで、出力部のリセットレベルを決めるとともに、出力トランジスタのゲートの電圧になります。VRDは、VODと同様に電圧ゲインやMOSFETの動作領域を決定し、出力部の飽和電荷量に影響します。VRDを大きくするとFDの電位も大きくでき信号量としては増加しますが、出力トランジスタで①②の現象が発生することを考慮して最適な値にする必要があります。

#### ▲ OGに加えるバイアス (Vog)

Vocは、水平シフトレジスタの最終部に配置されたFDと最終のクロッキングゲート(サミングゲート)を分離するためのOGに加えるバイアスです。信号電荷は、最終のクロッキングゲートであるサミングゲートパルス(SG)のLowレベルへの立ち下がりに同期してFDに出力されます。したがってOGの電位は、SGがLowレベルになったときの電位よりも小さくなり、OGの電位とリセット時の電位差が取り扱い可能な信号電荷量を決める要因になります。図3-6からも明らかなように、信号電荷量は、OG下の電位とリセットゲートのLowレベル時の電位のいずれかで制限されます。Vogが低いほど、出力部の飽和電荷量は大きくなりますが、低すぎる場合にはSGのLowレベル時に信号電荷がFDに流入できなくなるため、Vogは適切な値に調整する必要があります。

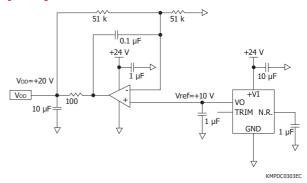

#### ☑ バイアス電圧発生回路

バイアス電圧は、主にCCDの出力アンプ周辺部に印加されます。したがって、電源は比較的ノイズの少ない安定したものを使用してください。また、電圧精度・電圧変動・リップル・出力電流などに注意することも重要です。

図3-7にOD端子のバイアス電圧発生回路の例を示しま

す。基準電圧は電源ICより生成し、ローパスフィルタを構成する増幅器で所定の電圧値にしています。これにより、低ノイズで高安定・高精度の電圧が得られます。

#### [図3-7] バイアス電圧発生回路の例

# 3-3 信号処理回路

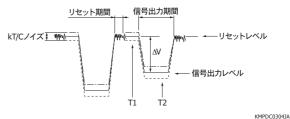

CCDのノイズの主な要因には、一般的によく知られているkT/Cノイズと1/fノイズがあります。kT/Cノイズは、FDA(「1-3 FDA」参照)における電荷放電(リセット動作)によって生じます。このノイズはFDAのノード容量(Cfd)の平方根に反比例し、CCDの全ノイズに対して大きな比率を占めます。また、1/fノイズはFDAを構成するMOSFETで発生するノイズで、周波数に反比例します。

これらのノイズはCCDシステムのS/Nを悪化させるため、信号処理回路においてできる限り減らすように工夫する必要があります。その代表的な回路がCDS回路です。

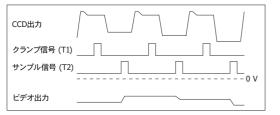

CDS回路の動作原理について説明します。図3-8は CCDの出力波形を示しています。前述の通りFDAにおけるリセット期間中にkT/Cノイズが発生します。このため、リセット期間が終了した時点の電圧レベルはkT/Cノイズによって変動します。したがって、時間 T2においてデータを取得した場合、kT/Cノイズの変動分がS/Nを悪化させます。これに対して、出力波形の時間 T1と時間 T2でデータを取得し、その差を取ることでkT/Cノイズが除去された信号分 ΔVのみを取り出すことができます。このとき、オフセット電圧分や、リセットフィードスルーなどのDC 成分も同時に取り除かれます。

#### [図3-8] CCDの出力波形

&去ールド

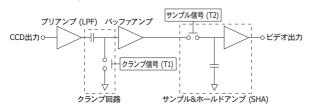

CDS回路には「①クランプ回路とサンプル&ホールドアンプ(以下、SHA)を組み合わせた方式」と、「②SHAと

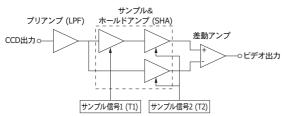

差動アンプを組み合わせた方式」があります。①の方式 [図3-9]は、非常に単純な回路構成ですが、クランプ回路に使用するスイッチのオン抵抗が大きい場合、除去されるノイズ量が少なくなったり、DC電圧誤差を生じたりします。なお、オン抵抗は0Ωであることが理想的です。

#### [図3-9] CDS回路 (クランプ回路とSHAを組み合わせた 方式)のブロック図

KMPDC0305JA

②の方式 [図3-10]は、部品点数が多くなりますが、① の方式に比べてノイズの除去効果は高くなります。しかし、 SHA出力をアナログ的に演算するため、SHA自体のもつノイズが加算され、ノイズが多くなる場合があります。SHAの ノイズはkT/Cノイズが無視できる程度に小さい必要があります。

# [図3-10] CDS回路 (SHAと差動アンプを組み合わせた方式)のブロック図

KMPDC0306JA

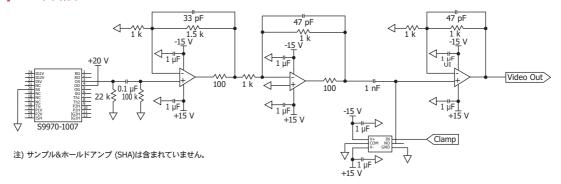

図3-11に①の方式を採用した回路例を示します。

プリアンプではCCDの出力を十分に増幅するためゲインを高くします。CCDの出力にはDC電圧成分を含んでいるため、コンデンサでAC結合します。しかし、プリアンプのバイアス電流が大きい場合、このコンデンサによって大きなDC電圧誤差を生じます。したがってバイアス電流の小さなアンプを選択する必要があります。一般的にはJFETもしくはCMOS入力型アンプを使用します。またCCDの出力波形を増幅できる十分な帯域をもった低ノイズのアンプを選択する必要があります。

クランプ回路はコンデンサとアナログスイッチにて構成します。アナログスイッチについては、低オン抵抗でチャージインジェクション量の小さな高速タイプを推奨します。

最終段のアンプは、プリアンプと同様にコンデンサによるAC結合となるため、JFETまたはCMOS入力型を選択します。また、入力インピーダンスが高くなるように非反転増幅器を構成します。

ところで、CCDの出力は負極性であり、アナログーデジタル変換を容易にするために最終段アンプの出力を正極性とします。このため、プリアンプの後段に反転増幅器を接続します。

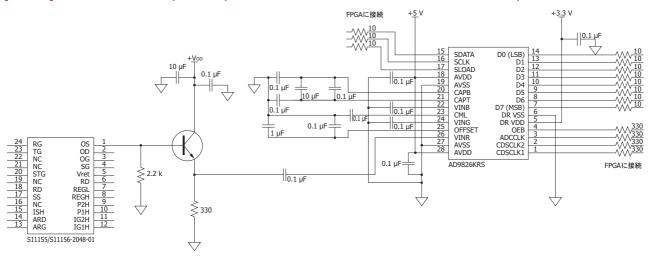

## 3-4 高速信号処理回路

数MHz以上の読み出し速度が必要とされるCCDの信号処理回路において、ディスクリート部品だけで構成された回路ではクランプの高速動作やコンデンサへの速い充放電特性を実現することは困難です。

CCDの信号処理に最適化されたアナログフロントエンドIC (CDS/ゲイン/オフセット回路、A/D変換器などを1チップで構成したIC)を使用することで高速信号処理回路を構成できます。

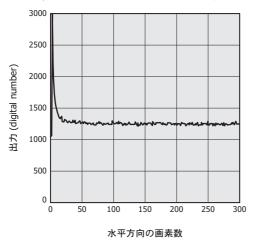

# 3-5 出力回路における発光の対策

2段MOSFETソースフォロワを採用しているCCDの出力回路において、動作条件が適切でない場合、アンプが発光することがあります。この発光をレジスティブゲートやストレージゲート、水平シフトレジスタで受光すると、暗状態においても読み始めの画素で出力が大きくなる現象が発生します「図3-14」。

この影響を減らすためには以下の対策が有効です。

- ① Vret端子に+1 V typ.の電圧を印加する (Vret端子 がある場合)。

- ② 水平シフトレジスタクロックパルス (P1H, P2H)を振幅 の50% ± 10%で交差させる [図3-15]。

- ・水平2相駆動の場合: P1H, P2H

- ・水平4相駆動の場合: P1H, P3HおよびP2H, P4H

- ③全画素の読み出し後、TGがHighレベルになる直前まで水平方向の空読み出しを行う。

#### [図3-11] CDS回路例

#### [図3-12] 高速信号処理回路例 (S11155/S11156-2048-01とアナログフロントエンドICを使用)

#### [図3-13] タイミングチャート (S11155-2048-01)

\*空読み出し期間中は所定の端子にクロックパルスを印加してください。 蓄積時間に応じて、全クロックパルス数 Nを設定してください。

KMPDC0382JB

KMPDC0053JD

#### [図3-14] 出力回路における発光の影響 (暗状態における水平プロファイル, 代表例)

KMPDB0328JA

#### [図3-15] 水平シフトレジスタクロックパルスの波形

比較的長い蓄積をする場合には、水平シフトレジスタで発生する電荷を捨てるために、全画素の読み出し後にトランスファーゲートへの転送を開始する直前まで空読み出しを行います。この方法は、蓄積時間中に水平シフトレジスタで発生する電荷を捨てる場合にも有効です。

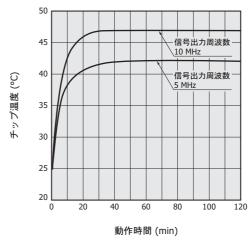

# 3-6 チップ温度

図3-16は当社製評価回路を用いてS11155-2048-01を動作させたときのチップ温度と動作時間の関係を示した測定例です(回路系は密閉されており、放熱対策が施されていない状態)。高速動作させた場合は、チップ温度の上昇が顕著になります。チップ温度の上昇は暗電流の増加を招くため、放熱器の取り付けや送風などの放熱対策を行うことを推奨します。

#### [図3-16] チップ温度ー動作時間 (S11155-2048-01, 当社製評価回路を使用, 代表例)

KMPDB0594JB

# 3-7 補正

一般にイメージセンサには、画素間においてフォトン (光子)に対する感度の不均一性 (PRNU)と、設定した動作条件における暗電流の不均一性 (DCNU: Dark Current Nonuniformity)があります。高精度のデータを収集するためには、少なくともこれらの2つの不均一性を補正する必要があります。不均一性は温度によって値が変わります。そのため、温度を考慮に入れた上で補正する必要があります。

#### (1) 暗電流の補正

暗電流は画素によって異なるため、高精度に補正する ためには画素単位で考える必要があります。光の入射が ないときのCCDの暗電流 (Nt)は式 (3-1)で表されます。

$Nt(x, y, t, T) = Nd(x, y, T) \times t + Nb(x, y, T) \cdots (3-1)$

x : 水平方向のアドレス y : 垂直方向のアドレス t : 蓄積時間 T : CCDの温度

Nd(x, y, T): 各画素の暗電流 [e<sup>-</sup>/pixel/s] Nb(x, y, T): 蓄積時間ゼロのときの暗電流

蓄積時間がゼロのときの暗電流 Nb(x, y, T)は、オフセットやバイアスとも呼ばれます。この値は、動作条件によって変わります。当社のデータシートに記載された暗電流値は、Nd(x, y, T)をある領域で平均した暗電流であり、実際にCCDから出力される暗電流とは異なります。補正のためには、NdとNbの両方を取得する必要があります。NdやNbは1回の読み出しデータから取得できますが、外乱ノイズの影響を除くためには数回から10回程度、画像を取得して平均化すれば、より精度の高い補正画像データが得られます。

#### (2) フラットフィールド補正

「2-4 感度不均一性」で示したように、CCDの感度は各画素で均一でないため、暗電流と同様に画素単位で補正する必要があります。ある露光条件での補正されていない出力 I(x, y)は、式 (3-2)で表されます。

$$I(x, y) = Nt(x, y, t, T) + i(x, y) \times r(x, y) \cdots (3-2)$$

i(x, y): 元画像の出力 r(x, y): 各画素の感度

元画像の出力 i(x, y)を得るためには、暗電流 (Nt)とともにr(x, y)を知る必要があります。通常は、CCDに非常に均一な光を入射して、そのときの出力を取ることでr(x, y)が得られますが、均一な光を入射することは困難です。また、CCDの受光部上の位置によって波長ごとの感度が異なることがあります。1%以下の精度で補正するためには、光学系や温度などに注意して補正データを取得する必要があります。r(x, y)は、1回の読み出しデータでも取得できますが、外乱ノイズの影響を除くためには、数回から10回程度、画像を取得して平均化すれば、より精度の高い校正データが得られます。

# 3-8 FOSとのカップリング

表面入射型CCDにFOS (Fiber Optic plate with Scintillator)をカップリングして数十keV以上のX線を検出することができます。

# 3-9 放射線損傷

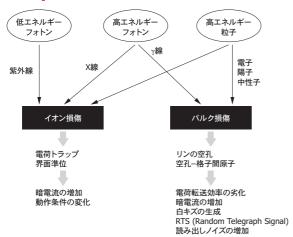

Siを使った他のデバイスと同じように、CCDも放射線によってイオン損傷とバルク(bulk)損傷を生じます。CCDをX線検出に使用したり、宇宙環境で用いる場合には、放射線損傷についてあらかじめ考慮しておく必要があります。

#### [図3-17] 放射線によるCCDへの影響

イオン損傷は、あるレベル以上のエネルギー(おおむ ね紫外線よりエネルギーが高い場合)のフォトンが入射 しゲート酸化膜内で電子-正孔対が生成されたときに 発生します。フォトンにより発生した電子-正孔対のほと んどは再結合して消滅しますが、電子に比べて移動度 の小さな正孔の一部は酸化膜中でトラップされ、CCDの 動作ゲート電圧をシフトさせるような電圧を発生させま す。これによってCCDのピンニング電圧がより負側に移 動します(シフト量が数Vになる場合もあります)。高エネ ルギーの電子あるいはフォトンが入射すると、イオン損傷 とバルク損傷を引き起こします。一方、陽子や中性子のよ うな重粒子も、ゲート絶縁膜中で電荷を発生させます。 電子やフォトンは、酸化膜界面において新たな界面準位 を発生させます。その界面準位のエネルギーレベルはバ ンドギャップ中にあるため、暗電流が増加することになり ます。

バルク損傷は、陽子のようなエネルギーを帯びた荷電 粒子がSi原子と相互作用するときに発生します。陽子に 十分なエネルギーがあると、Si原子を格子状の位置から 格子間の位置に置き換えます(これが発生するには約 100 eVのエネルギーが必要です)。置き換えられたSi原 子は、他のSi原子と衝突してさらに多くの原子を置き換 えます。これにより生じた欠陥は、電子のトラップとして 働きます。CCDの電荷転送チャンネル内に多くのトラップ が作られると、電荷転送効率(CTE)が劣化します。生成 された欠陥は、暗電流の大きい画素となります。

#### [図3-18] X線による損傷 (S9970-0907, 代表例)

KMPDB0243JB

# 3 - 10 放熱

#### (1) 放熱器の選択

電子冷却型CCDを使用する場合には、十分な放熱能力をもった放熱器を選択する必要があります。

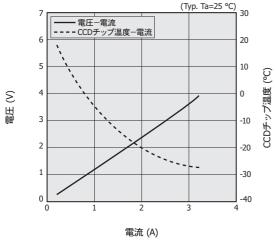

#### [図3-19] 1段電子冷却素子の温度特性 (S7031-1006S/-1007S, CCD未駆動)

KMPDB01793

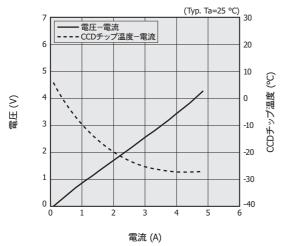

#### [図3-20] 2段電子冷却素子の温度特性 (S7032-1007, CCD未駆動)

KMPDB03843

#### (2) 装置の設計

放熱器で発生した熱が十分放熱されるように装置を 設計する必要があります。エアファンや通気ダクトを配置 した通風のある設計を行ってください。

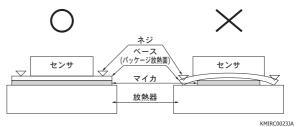

#### (3) 放熱器の取り付け方法

冷却能力を十分に発揮させるためには、製品と放熱 器を正しく接着する必要があります。以下の点に注意し て放熱器を取り付けてください。

- ・製品の放熱面と放熱器の接着面がきれいで平坦であることを確認してください。

- ・電子冷却素子による冷却時の放熱が不十分な場合、素子温度が高くなり製品に物理的な損傷を与える可能性があります。冷却時には十分な放熱を行ってください。放熱方法としては、製品と放熱器の間に熱伝導性の高い材料(例:富士高分子工業社製放熱シリコーンゲルGR-d、東レ・ダウコーニング社製放熱シリ

コーン SE 4490 CV、住友スリーエム社製熱伝導シート 5580Hなど)を挟むことを推奨します。これらの熱伝導 材を使用する場合、製品と放熱器の接合部の全面に 均一な厚さで塗布してください。また、マイカなどを使用する場合にも、パッケージ放熱面の全面が接触する ようにしてください。もし、ネジ止め位置までマイカの寸 法がないままネジ止めした場合、冷却効果が下がるだけでなく、ベースがそり、センサとベースの間でクラックが発生することがあります [図3-21]。

- ・製品を基板などに挿入する際、受光窓を絶対に押さないでください。受光窓にひび・割れが生じたり脱落する可能性があり、故障の原因となります「図3-22」。

- ・放熱器に製品をネジ止めする場合、トルクは0.3 N·m 以下に設定し、製品に均等な応力がかかるように2箇 所のネジを交互に締めてください。

#### [図3-21] 放熱器への取り付け方法

#### [図3-22] 基板への取り付け方法

#### (4) 電子冷却素子への供給電流

電子冷却素子を保護し安定した動作を維持するために、電子冷却素子への供給電流はデータシートに定められた最大電流の60%以下に設定してください。

# 3-11 静電気/サージ対策

CCDは、静電気やサージにより破壊もしくは劣化する危険性がありますので、以下の点に十分注意してください。

#### (1) 取扱上の注意

CCDを梱包ケースから取り出す際は、静電気対策をした場所にて行います。作業台・床は、導電性シート (1  $M\Omega\sim100~M\Omega$ )を敷いて接地してください。

CCDを取り扱う作業者は、必ずリストバンドを装着し、静電気防止対策のされた作業服・手袋・靴などを着用してください。リストバンドは、必ず人体側に保護抵抗(1 MΩ程度)入りのものを使用し、接地してください。保護抵抗がない場合は、漏電によって感電する恐れがあり、非常に危険です。

はんだごては、漏洩電圧が加わらないように必ず接地 する必要があります。

CCDに帯電物(プラスチック、ビニールなどの絶縁物、PCのVDTなど)を近づけないでください。近づけるだけでCCDが帯電し、放電破壊を起こす危険性があります。

#### (2) 使用上の注意

測定器や治工具などは、必ずアースに接続して、漏洩電圧によりサージが加わらないようにしてください。CCDには、測定器などから絶対最大定格を超えた電圧が加わらないようにしてください(特に電源のオン・オフ時に起こりやすいので注意する必要があります)。サージが加わる恐れのある場合は、フィルタ(抵抗・コンデンサで構成)を入れて保護してください。

CCDの逆挿入・誤挿入・端子間ショートをしないように 十分注意してください。

動作中は、電源ラインや出力ラインに接続されているコネクタなどを付けたり外したりしないでください。

#### (3) 運搬上の注意

CCDは、導電性のマットに挿して(リードを短絡)、導電性の容器に入れて運搬してください。実装基板は、導電性の容器に入れて運搬してください。プラスチック・発泡スチロールなどにCCDを入れて運搬すると、振動などで静電気が発生し、劣化もしくは破壊の原因となります。

#### (4) 保管上の注意

CCDは、導電性のマットに挿して(リードを短絡)、導電性の容器に入れて保管してください。実装基板は、導電性の容器に入れて保管してください。

高電圧・高電磁界を発生する機器の近くにCCDを置かないでください。

以上のような静電気/サージ対策は、必ずしもすべて 実施しなければならないということではありませんが、劣 化もしくは破壊の発生状況に応じて実施してください。

# 4. 応用製品

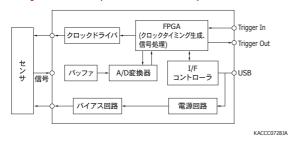

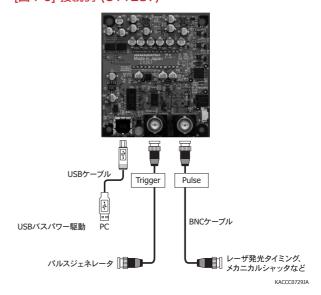

当社のCCDイメージセンサを簡単に動作させて、各種装置に組み込んで使用できるように、ボードタイプの駆動回路や筐体に内蔵されたマルチチャンネル検出器へッドを用意しています。駆動回路は小型・安価で装置への組み込みが容易です [図4-1]。また、駆動回路には、機能の異なる基板を積み上げるスタック型もあります。必要な機能の基板を取り外して使用したり、基板を取り換えたりすることができます。センサ専用の小型基板がフラットケーブルで接続されたタイプでは、センサを柔軟に配置できます [図4-2]。

マルチチャンネル検出器ヘッドでは、センサと駆動回路の放熱に配慮しており、光学系との接続が容易です。 レンズマウントアダプタをオプションとして用意しているものもあります(別売)[図4-3]。

これらの駆動回路や検出器ヘッドは、主に以下で構成され、イメージセンサの特性を最大限に生かすように設計されています。

#### ・イメージセンサ制御部

(バイアス回路、クロッキング回路、信号処理回路)

・デジタル制御部

(イメージセンサ駆動用タイミング回路、CPU、メモリ)

- ・インターフェース制御部 (USB, Cameralink)

- •電子冷却制御部 (温度制御回路)

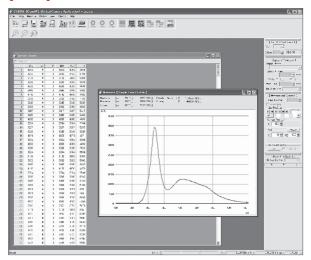

付属のアプリケーションソフトウェアを使うことによって、PCで各種パラメータの設定、データ取得・解析などを簡単に行うことができ、センサを含めた回路の特性評価を短時間で効率よく行うことが可能です。

なお、形状・サイズ・機能・インターフェースなどについて、カスタム対応も可能です。

[図4-1] 駆動回路 C11165-02 (CCDリニアイメージセンサ用)

# [図4-2] 駆動回路 (スタックタイプ) C15361シリーズ (CCDリニアイメージセンサ用)

#### [図4-3] マルチチャンネル検出器ヘッド C7041 (CCDエリアイメージセンサ用)

# 4-1 特長

- ・16ビット (または14ビット)高精度A/D変換器内蔵

- ・オフセット、ゲイン調整機能を内蔵

- ・さまざまな外部トリガモードによるデータ取得が可能

- ・USBやCamera Linkなど汎用インターフェースを搭載

- ・小型:装置への組み込みが可能

# 4-2 構成

#### [図4-4] ブロック図 (代表例: C11287)

# 4-3 使い方

付属のアプリケーションソフトウェアとドライバをPC にインストールするだけで、すぐにデータ収集が可能で す。関数ライブラリ (DLL)も付属しているため、ユーザ サイドで、Microsoft® Visual C++®、Microsoft Visual Basic®、LabVIEW®などの開発環境において、ソフトウェ ア開発を効率よく行うことができます。

Camera Linkタイプについては、市販のフレームグラバボードとCamera Link規格準拠のケーブルを用い、フレームグラバボード付属のアプリケーションソフトウェアおよびDLLを使用してユーザサイドで独自のソフトウェアの開発を行うことができます。

注)Microsoft、Visual C++、Visual Basicは、米国Microsoft Corporationの 米国およびその他の国における登録商標です。LabVIEWは、National Instruments社の登録商標です。

#### [図4-5] アプリケーションソフトウェア画面例

#### [図4-6] 接続例 (C11287)

# 5. 新たな取り組み

当社は、これまでに蓄積した技術に加え新しい技術を 応用して、新たなCCDを開発しています。

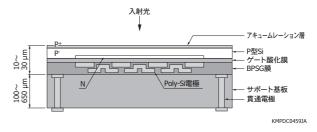

#### ◆ 全面薄型CCD

当社の裏面入射型CCDは、一部の近赤外高感度タイプを除き、部分薄型と呼ばれる、Siを部分的に薄くした構造です。部分薄型CCDは、受光部のSi厚が10~30μm程度のため大面積化は困難です。また、薄いSiを支えるために、厚いSiでその周囲を取り囲む必要があるため、受光部表面における遮光部の形成やFOPなどの実装が難しくなります。

このような問題を解決するために、当社では全面薄型 CCDの開発を行っています。全面薄型構造にするために、ウエハにサポート基板を貼り付けた後、ウエハ全面を薄くします。入射面側に電極が露出した形状 [図5-2(a)]と、サポート基板側に貫通電極がある形状 [図5-2(b)]の2種類を開発中です。全面薄型構造を採用することにより、チップの強度が高まり、大面積化が可能となるとともに、受光部表面への遮光部の形成やFOPなどの実装が容易となります。

#### [図5-1] 部分薄型CCDの構造

#### [図5-2] 全面薄型CCDの構造

#### (a) 入射面側に電極が露出した形状

#### (b) サポート基板側に貫通電極がある形状

#### ■ 参考文献

- Masaharu Muramatsu, Hiroshi Akahori, Katsumi Shibayama, Syunsuke Nakamura and Koei Yamamoto, Hamamatsu Photonics K. K., Solid State Division: "Greater than 90% QE in Visible Spectrum Perceptible from UV to near IR Hamamatsu Thinned Back Illuminated CCDs", SPIE, Solid State Sensor Arrays: Developments and Applications, 3019 (1997), P2

- M. P. Lesser, Steward Observatory, University of Arizona: "Chemical/ Mechanical Thinning Results", SPIE, New Methods in Microscopy and Low Light Imaging, 1161 (1989),P98

- James Janesic, Tom Elliott, Taher Daud, Jim McCarthy, Jet Propulsion Laboratory California Institute of Technology, Morley Blouke, Tektronix. Inc.,: "Backside charging of the CCD", SPIE, Solid State Imaging Arrays, 570 (1985), P46

本資料の記載内容は、令和2年11月現在のものです。

製品の仕様は、改良などのため予告なく変更することがあります。本資料は正確を期するため慎重に作成されたものですが、まれに誤記などによる誤りがある場合があります。本製品を使用する際には、必ず納入仕様書をご用命の上、最新の仕様をご確認ください。

本製品の保証は、納入後1年以内に瑕疵が発見され、かつ弊社に通知された場合、本製品の修理または代品の納入を限度とします。ただし、保証期間内であっても、 天災および不適切な使用に起因する損害については、弊社はその責を負いません。

本資料の記載内容について、弊社の許諾なしに転載または複製することを禁じます。

# 浜松ホトニクス株式会社

#### www.hamamatsu.com

| 仙台営業所  | 〒980-0021 | 仙台市青葉区中央3-2-1 (青葉通プラザ11階)        | TEL (022) 267-0121 FAX (022) 267-0135 |

|--------|-----------|----------------------------------|---------------------------------------|

| 筑波営業所  | 〒305-0817 | つくば市研究学園5-12-10 (研究学園スクウェアビル7階)  | TEL (029) 848-5080 FAX (029) 855-1135 |

| 東京営業所  | 〒105-0001 | 東京都港区虎ノ門3-8-21 (虎ノ門33森ビル5階)      | TEL (03) 3436-0491 FAX (03) 3433-6997 |

| 中部営業所  | 〒430-8587 | 浜松市中区砂山町325-6 (日本生命浜松駅前ビル)       | TEL (053) 459-1112 FAX (053) 459-1114 |

| 大阪営業所  | 〒541-0052 | 大阪市中央区安土町2-3-13 (大阪国際ビル10階)      | TEL (06) 6271-0441 FAX (06) 6271-0450 |

| 西日本営業所 | 〒812-0013 | 福岡市博多区博多駅東1-13-6 (いちご博多イーストビル5階) | TEL (092) 482-0390 FAX (092) 482-0550 |

固体営業推進部 〒435-8558 浜松市東区市野町1126-1 TEL (053) 434-3311 FAX (053) 434-5184