# **CMOS** area image sensor

S14250

# Near infrared high sensitivity, APS (active pixel sensor) type

The S14250 is an APS (active pixel sensor) type CMOS area image sensor featuring high sensitivity, small number of pixels, and low power consumption. Because the pixels are large ( $50 \times 50 \mu m$ ), data acquisition is possible even in low illuminance environment. Because there are only few pixels ( $30 \times 30 \mu m$ ), all the pixels can be read out at a maximum rate of 344 frames/s. The number of readout pixels can be reduced further through partial readout. The image sensor has a timing generator, bias generator, A/D converter, and serial peripheral interface (SPI), provides digital I/O, and can be driven by a single 3.3 V power supply. These features make it easy to handle. Low power consumption is provided. It consumes approx. 30 mW during imaging and 0.7 mW or less during standby through the power-down function.

#### Features

- Pixel size: 50 × 50 μm

- Number of pixels: 30 x 30

- → Global shutter readout

- **■** Single 3.3 V power supply operation

- SPI communication function (partial readout, gain switching, operation mode selection, etc.)

- → Partial readout function

# Applications

- Security camera (night vision, moving object detection)

- Monitoring camera (low resolution to accommodate privacy)

### Structure

| Parameter                                 | Specification                                 | Unit   |

|-------------------------------------------|-----------------------------------------------|--------|

| Image size (H × V)                        | 1.5 × 1.5                                     | mm     |

| Pixel size                                | 50 × 50                                       | μm     |

| Pixel pitch                               | 50                                            | μm     |

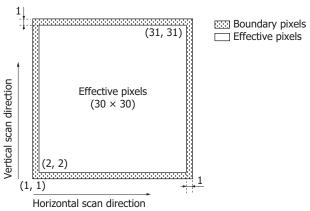

| Total number of pixels $(H \times V)$     | 32 × 32                                       | pixels |

| Number of effective pixels $(H \times V)$ | 30 × 30                                       | pixels |

| Boundary pixels                           | 1 column enclosing the effective pixel region | -      |

| Package                                   | Ceramic                                       | -      |

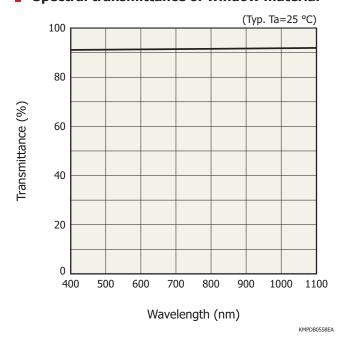

| Window material                           | Borosilicate glass                            | -      |

### Pixel layout

KMPDC0687EA

## **→** Absolute maximum ratings (Ta=25 °C)

| Parameter                               |                  | Symbol   | Condition             | Value                                       | Unit |

|-----------------------------------------|------------------|----------|-----------------------|---------------------------------------------|------|

| Cumply vallenge                         | Analog terminal  | Vdd(A)   |                       | -0.3 to +4.2                                | V    |

| Supply voltage                          | Digital terminal | Vdd(D)   |                       | -0.3 to +4.2                                | V    |

| Digital input signal terminal voltage*1 |                  | Vi       |                       | -0.3 to +4.2                                | V    |

| Vref_cp1 terminal voltage               |                  | Vref_cp1 |                       | -0.3 to +6.5                                | V    |

| Vref_cp2 terminal voltage               |                  | Vref_cp2 |                       | -2.0 to +0.3                                | V    |

| Operating temperature                   |                  | Topr     | No dew condensation*2 | -10 to +65                                  | °C   |

| Storage temperature                     |                  | Tstg     | No dew condensation*2 | -10 to +85                                  | °C   |

| Reflow soldering co                     | onditions        | Tsol     | JEDEC MSL 2a          | Peak temperature: 260 °C, 3 times (see P.9) | -    |

<sup>\*1:</sup> SPI\_CS, SPI\_SCLK, SPI\_MOSI, MCLK

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

## - Recommended operating conditions (Ta=25 °C)

| Parameter        |                  | Symbol | Min.          | Тур.    | Max.          | Unit |

|------------------|------------------|--------|---------------|---------|---------------|------|

| Supply voltage — | Analog terminal  | Vdd(A) | 3.0           | 3.3     | 3.6           | V    |

|                  | Digital terminal | Vdd(D) | 3.0           | Vdd (A) | 3.6           | V    |

| Digital input    | High level       | Vi(H)  | Vdd(D) - 0.25 | Vdd(D)  | Vdd(D) + 0.25 | W    |

| voltage*3        | Low level        | Vi(L)  | 0             | -       | 0.25          | V    |

<sup>\*3:</sup> SPI\_CS, SPI\_SCLK, SPI\_MOSI, MCLK

# **■** Electrical characteristics (Ta=25 °C)

| Digital input signal |  |

|----------------------|--|

[Operating conditions: Recommended operating conditions Typ.]

| Parameter                     | Symbol   | Min. | Тур. | Max. | Unit |

|-------------------------------|----------|------|------|------|------|

| Master clock pulse frequency  | f(MCLK)  | 1    | -    | 10   | MHz  |

| Master clock pulse duty cycle | D(MCLK)  | 45   | 50   | 55   | %    |

| Rise time*4 *5                | tr(sigi) | -    | 5    | 7    | ns   |

| Fall time*4 *5                | tf(sigi) | -    | 5    | 7    | ns   |

<sup>\*4:</sup> SPI\_CS, SPI\_SCLK, SPI\_MOSI, MCLK

# Digital output signal

[Operating conditions: Recommended operating conditions Typ.]

| - '                      |      |          | /· -          |        |      |      |

|--------------------------|------|----------|---------------|--------|------|------|

| Parameter                |      | Symbol   | Min.          | Тур.   | Max. | Unit |

| Data rate                |      | DR       | f(MCLK)/16    |        |      | Hz   |

| Digital output voltage*6 | High | Vsigo(H) | Vdd(D) - 0.25 | Vdd(D) | -    | V    |

|                          | Low  | Vsigo(L) | -             | 0      | 0.25 | V    |

| Rise time*6 *7           |      | tr(sigo) | -             | -      | 20   | ns   |

| Fall time*6 *7           |      | tf(sigo) | -             | -      | 20   | ns   |

<sup>\*6:</sup> PCLK, Vsync, Hsync, Dout, SPI\_MISO

<sup>\*2:</sup> When there is a temperature difference between a product and the surrounding area in high humidity environment, dew condensation may occur on the product surface. Dew condensation on the product may cause deterioration in characteristics and reliability.

<sup>\*5:</sup> Time for the input voltage to rise or fall between 10% and 90%

<sup>\*7:</sup> Time for the output voltage to rise or fall between 10% and 90% when there is a 10 pF load capacitor is attached to the output terminal

### Current consumption

[Operating conditions: Recommended operating conditions Typ., digital input signal Typ.]

| Parameter                                       |                    | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|--------------------|--------|------|------|------|------|

|                                                 | Analog terminal*8  | I1     | -    | 5    | 7    | mA   |

| Single imaging mode,<br>Continuous imaging mode | Digital terminal*8 | I2     | -    | 3    | 4    | mA   |

| Low power                                       | Analog terminal*8  | I1(ps) | -    | 1    | 2    | μΑ   |

| consumption mode                                | Digital terminal*8 | I2(ps) | -    | 120  | 200  | μΑ   |

<sup>\*8:</sup> Dark state, master clock pulse frequency=10 MHz, frame rate=344 frames/s

#### A/D converter

[Operating conditions: Recommend operating conditions Typ. (P.2), digital input signal Typ. (P.2)]

| Parameter                  | Symbol | Specification | Unit |

|----------------------------|--------|---------------|------|

| Resolution                 | Reso   | 10 or 12      | bit  |

| Conversion time            | tcon   | 16/f(MCLK)    | S    |

| Conversion voltage range*9 | -      | 0 to 1.2      | V    |

<sup>\*9:</sup> Default value

# **=** Electrical and optical characteristics

# [Ta=25 °C, recommend operating conditions Typ., digital input signal Typ., MCLK=10 MHz, gain: initial setting]

|                              |                   |         | v                       |                         |      |          |

|------------------------------|-------------------|---------|-------------------------|-------------------------|------|----------|

| Parameter                    |                   | Symbol  | Min.                    | Тур.                    | Max. | Unit     |

| Spectral response            | range             | λ       |                         | 400 to 1100             |      | nm       |

| Peak sensitivity wa          | velength          | λр      | -                       | 700                     | -    | nm       |

| Photoresponse nor            | nuniformity*10    | PRNU    | -                       | -                       | ±10  | %        |

| Defective nivels             | White spot*11     | WS      | -                       | -                       | 0    | pixels   |

| Defective pixels             | Black spot*12     | BS      | -                       | -                       | 0    | pixels   |

| Offset output*13             |                   | Voffset | 0.8                     | 1.1                     | 1.4  | V        |

| Dark output*13               |                   | DS      | -                       | 400                     | 1200 | mV/s     |

| Dark output variati          | on* <sup>14</sup> | DSNU    | -                       | 100                     | 300  | mV/s rms |

| Saturation output voltage*15 |                   | Vsat    | 0.8                     | 1.1                     | -    | V        |

| Red sensitivity*16           |                   | Sred    | 1.06 × 10 <sup>14</sup> | 1.52 × 10 <sup>14</sup> | -    | V/(W·s)  |

| Random noise*13              |                   | RN      | -                       | 4                       | 7    | mV rms   |

| Dynamic range*17             |                   | Drange  | 41                      | 49                      | -    | dB       |

<sup>\*10:</sup> Output nonuniformity when white uniform light at approximately 50% saturation is applied.

It is calculated excluding boundary pixels and is defined as follows:

$PRNU = (\Delta X/X) \times 100 [\%]$

$\Delta X$ : difference value between the maximum output pixel and minimum output pixel

X: average output of all pixels

- \*11: Pixels whose dark output exceeds 2400 mV/s (excluding boundary pixels)

- \*12: Pixels whose output value is 50% or less than that of adjacent pixels when uniform white light is applied at approximately 50% saturation level (excluding boundary pixels)

- \*13: Average output of all pixels excluding boundary pixels under light-shielded condition

- \*14: Standard deviation of dark output of all pixels excluding boundary pixels

- \*15: Average of values obtained by subtracting the pixel offset outputs from the outputs produced when light is applied at a level equivalent to twice the saturation exposure (excluding boundary pixels)

- \*16: λ=630 nm

- \*17: Ratio of saturation output to random noise

# Spectral response (typical example)

# **Spectral transmittance of window material**

# Block diagram

HAMAMATSU PHOTON IS OUR BUSINESS

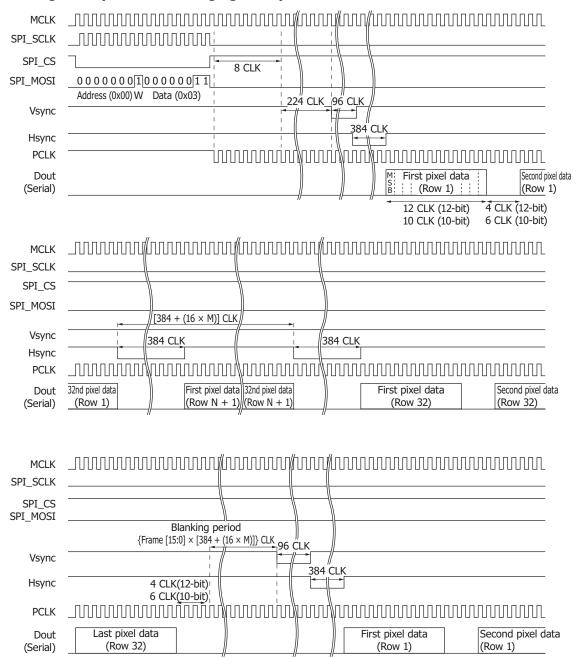

# Timing chart (continuous imaging mode)

M=number of columns

KMPDC0737EC

# **⇒** Setting using the SPI and the like

The following parameters can be set using the serial peripheral interface (SPI).

| Parameter                                     |                                                        | Mode and explanation                                                                                                                                         |  |  |

|-----------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                               | Imaging standby mode                                   | Supplies power to the analog circuit such as the bias circuit, in addition to the SPI. Imaging is not performed.                                             |  |  |

| Operation mode                                |                                                        | Integration starts as soon as a switch is made into this mode. When the integration over the period specified through SPI is complete, the data is read out. |  |  |

| Operation mode                                | Continuous imaging mode                                | Image data is output continuously.                                                                                                                           |  |  |

|                                               | Low power consumption mode                             | Stops all circuits except the SPI to suppress power consumption.                                                                                             |  |  |

| Integration time                              | Sets the integration                                   | i time.                                                                                                                                                      |  |  |

| Blanking period                               | Sets the blanking p                                    | eriod between frames.                                                                                                                                        |  |  |

| Readout region                                | Sets the readout re                                    | gion at the pixel level.                                                                                                                                     |  |  |

| Voltage conversion range of the A/D converter |                                                        | mit can be set between 0.8 to 1.55 V and the upper voltage limit between 1.8 to 2.55 V. r voltage limit=1.0 V, upper voltage limit=2.2 V                     |  |  |

| A/D converter resolution                      | Set it to 10-bit or 12-bit.<br>Initial setting: 12-bit |                                                                                                                                                              |  |  |

| Output gain                                   | Sets x1 or x4.<br>Initial setting: 4 times             |                                                                                                                                                              |  |  |

# ■ SPI register map

| Address              | Symbol    | Bit   | Description                                                                                                                                          |

|----------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

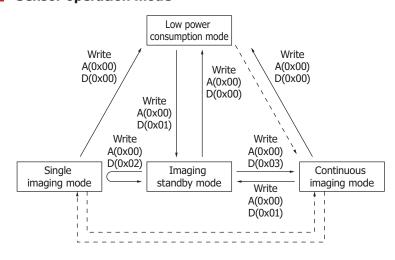

|                      | Mode      | [1:0] | Mode selection register                                                                                                                              |

| Read/Write<br>(0x00) | Msel2     | 1     | [00] Low power consumption mode [01] Imaging standby mode                                                                                            |

|                      | Msel1     | 0     | [10] Single imaging mode<br>[11] Continuous imaging mode                                                                                             |

| Read/Write (0x01)    | Integ_U   | [7:0] | Sets the integration time (upper bits). Initial setting: [00000000]                                                                                  |

| Read/Write<br>(0x02) | Integ_L   | [7:0] | Sets the integration time (lower bits). Initial setting: [00011111]                                                                                  |

| Read/Write (0x03)    | Frame_U   | [7:0] | Sets the blanking period between frames (upper bits). Initial setting: [00000000]                                                                    |

| Read/Write<br>(0x04) | Frame_L   | [7:0] | Sets the blanking period between frames (lower bits). Initial setting: [00000010]                                                                    |

| Read/Write (0x05)    | Start_row | [4:0] | Sets the address of the readout start row. Initial setting: [00000]                                                                                  |

| Read/Write<br>(0x06) | Start_col | [4:0] | Sets the address of the readout start column.  Initial setting: [00000]                                                                              |

| Read/Write (0x07)    | Numb_row  | [4:0] | Sets the number of readout rows. Initial setting: [11111]                                                                                            |

| Read/Write<br>(0x08) | Numb_col  | [4:0] | Sets the number of readout columns. Initial setting: [11111]                                                                                         |

|                      | ADC       | [7:0] | Sets the voltage conversion range of the A/D converter.<br>Initial setting: [10000100]=1.0 to 2.2 V (1.2 V)                                          |

| Read/Write (0x09)    | VRT       | [7:4] | Sets the upper voltage limit for A/D conversion. The value can be set in steps of 0.05 V. [0000]=1.8 V, [1111]=2.55 V, initial setting: [1000]=2.2 V |

|                      | VRB       | [3:0] | Sets the lower voltage limit for A/D conversion. The value can be set in steps of 0.05 V. [0000]=0.8 V, [1111]=1.55 V, initial setting: [0100]=1.0 V |

|                      | Gain      | [1:0] | Sets the analog amplifier gain and A/D converter resolution. Initial setting: [00]                                                                   |

| Read/Write<br>(0x0a) | Ampgain   | 1     | Set the analog amplifier gain. 1=x1 gain, 0=x4 gain, initial setting: 0                                                                              |

|                      | Reso      | 0     | Sets the A/D converter resolution.<br>1=10-bit, 0=12-bit, initial setting: 0                                                                         |

| Readonly<br>(0x0b)   | TEST      | [7:0] | SPI readout operation test register Fixed value: [10101010]                                                                                          |

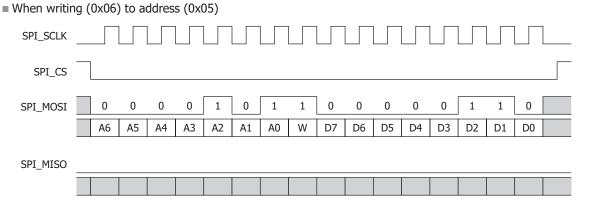

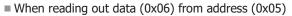

## **■** SPI setting example

KMPDC0734EA

KMPDC0735EA

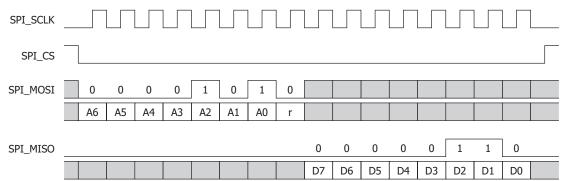

### Sensor operation mode

Note: Do not make a transition toward the broken lines.

KMPDC0736EA

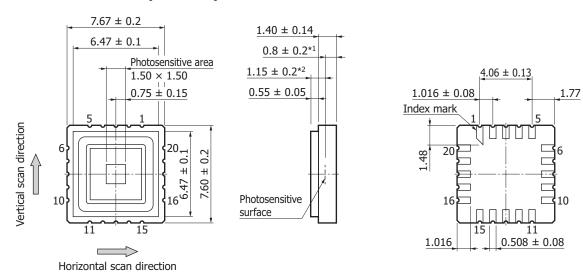

# Dimensional outline (unit: mm)

Tolerance unless otherwise noted: ±0.2

- \*1: Distance from package bottom to photosensitive surface

- \*2: Distance from glass surface to photosensitive surface

KMPDA0600ED

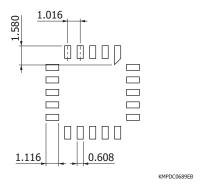

# - Recommended land pattern (unit: mm)

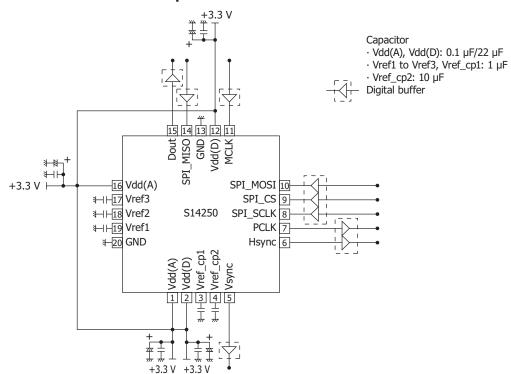

#### **₽** Pin connections

| Pin no. | Symbol   | Description                                     | I/O |

|---------|----------|-------------------------------------------------|-----|

| 1       | Vdd(A)   | Analog supply voltage*18 *19                    | I   |

| 2       | Vdd(D)   | Digital supply voltage*18 *19                   | I   |

| 3       | Vref_cp1 | Bias voltage for the charge pump circuit*20 *21 | I   |

| 4       | Vref_cp2 | Bias voltage for the charge pump circuit*21 *22 | I   |

| 5       | Vsync    | Frame sync signal                               | 0   |

| 6       | Hsync    | Line sync signal                                | 0   |

| 7       | PCLK     | Pixel output sync signal                        | 0   |

| 8       | SPI_SCLK | SPI clock signal* <sup>23</sup>                 | I   |

| 9       | SPI_CS   | SPI selection signal*24                         | I   |

| 10      | SPI_MOSI | SPI input signal* <sup>23</sup>                 | I   |

| 11      | MCLK     | Master clock signal                             | I   |

| 12      | Vdd(D)   | Digital supply voltage*18 *19                   | I   |

| 13      | GND      | Ground                                          | I   |

| 14      | SPI_MISO | SPI output signal                               | 0   |

| 15      | Dout     | Video output signal                             | 0   |

| 16      | Vdd(A)   | Analog supply voltage*18 *19                    | I   |

| 17      | Vref3    | Reference voltage*20                            | 0   |

| 18      | Vref2    | Reference voltage*20                            | 0   |

| 19      | Vref1    | Reference voltage*20                            | 0   |

| 20      | GND      | Ground                                          | I   |

<sup>\*18:</sup> To reduce noise, insert a capacitor around 0.1 µF and 22 µF between each terminal and GND.

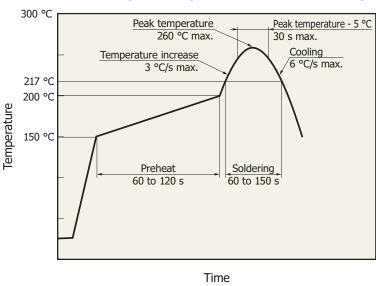

# - Recommended temperature profile for reflow solderings (typical example)

KMPDB0405EB

- This product supports lead-free soldering. After unpacking, store it in an environment at a temperature of 30 °C or less and a humidity of 60% or less, and perform soldering within 4 weeks.

- The effect that the product receives during reflow soldering varies depending on the circuit board and reflow oven that are used. When you set reflow soldering conditions, check that problems do not occur in the product by testing out the conditions in advance.

<sup>\*19:</sup> Apply voltage to all supply voltage terminals.

<sup>\*20:</sup> To reduce noise, insert a capacitor around 1 µF between each terminal and GND.

<sup>\*21:</sup> A terminal for monitoring the bias voltage generated inside the chip

<sup>\*22:</sup> To reduce noise, insert a capacitor around 10 µF between each terminal and GND.

<sup>\*23:</sup> When the SPI is not used, connect to GND.

<sup>\*24:</sup> When the SPI is not used, connect to Vdd.

#### Recommended baking conditions

See Precautions (surface mount type products).

#### Precautions

#### (1) Electrostatic countermeasures

This device has a built-in protection circuit against static electrical charges. However, to prevent destroying the device with electrostatic charges, take countermeasures such as grounding yourself, the workbench and tools. Also protect this device from surge voltages which might be caused by peripheral equipment.

#### (2) Light input window

If dust or stain adheres to the surface of the light input window glass, it will appear as black spots on the image. When cleaning, avoid rubbing the window surface with dry cloth, dry cotton swab or the like, since doing so may generate static electricity. Use soft cloth, a cotton swab, or the like moistened with alcohol to wipe dust and stain off the window surface. Then blow compressed air onto the window surface so that no dust or stain remains.

#### (3) Soldering

To prevent damaging the device during soldering, take precautions to prevent excessive soldering temperatures and times. Soldering should be performed within 5 seconds at a soldering temperature below 260 °C.

#### (4) Reflow soldering

Soldering conditions vary depending on the size of the circuit board, reflow oven, and the like. Check the conditions advance before soldering. Note that the bonding portion between the ceramic base and the glass may discolor after reflow soldering, but this has no adverse effects on the hermetic sealing of the product.

#### (5) UV light irradiation

This product is not designed to resist characteristic deterioration under UV light irradiation. Do not apply UV light to it.

#### Connection circuit example

KMPDC0690EA

#### Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- Disclaimer

- · Precautions / Image sensors

- · Precautions / Surface mount type products

Information described in this material is current as of August 2025.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use. Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

# AMAMATSU

www.hamamatsu.com

Optical Semiconductor Sales, HAMAMATSU PHOTONICS K.K.

1126-1 Ichino-cho, Chuo-ku, Hamamatsu City, Shizuoka Pref., 435-8558 Japan, Telephone: (81)53-434-3311, Fax: (81)53-434-5184

1126-1 ICRIRO-CRO, CRUO-KU, Hamamatsu City, Strizulord Freit, 4:32-6:305 Jajult, Telephone: (1)908-231-1218

Germany: HAMAMATSU CORPORATION: 360 Foothill Road, Bridgewater, NJ 08807, U.S.A., Telephone: (1)908-231-231-0960, Fax: (1)908-231-1218

Germany: HAMAMATSU PHOTONICS DEUTSCHLAND GMBH: Arzbergersts. 10, 82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-265-8 E-mail: info@hamamatsu.de

France: HAMAMATSU PHOTONICS FRANCE S.A.R.L.: 19 Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10 E-mail: info@hamamatsu.df

United Kingdom: HAMAMATSU PHOTONICS IX LIMITED: 2 Howard Court, 10 Tewin Road, Welwyn Gand, Howeyn Garlier, ALT 18W, UK, Telephone: (44)1707-294888, Fax: (44)1707-295777 E-mail: info@hamamatsu.co.uk

North Europe: HAMAMATSU PHOTONICS NORDEN AB: Torshamnsgatan 35, 1640 Kista, Sweden, Telephone: (46)8-509-031-00, Fax: (46)8-509-031-10. Fax: 12 He-mail: info@hamamatsu.df

Litaly: HAMAMATSU PHOTONICS ITALIA S.R.L.: Strada della Mola, 1 int. 6 20044 Arese (Milano), Italy, Telephone: (46)8-509-031-01, Fax: (39)02-93 58 17 41 E-mail: info@hamamatsu.df

Litaly: HAMAMATSU PHOTONICS (CHINA). CO, LTD: 1201, Tower B, Jianining Center, 27 Dongsanhuan Bellu, Chaoyang District, 100020 Beijing, RR. China, Telephone: (86)10-6586-6006, Fax: (86)10-6586-6006, Fax:

Korea: HAMAMATSU PHOTONICS KOREA CO., LTD.: A-912, 167, Songpa-daero, Seoul, 05855, Korea, Telephone: (82)2-2054-8202, Fax: (82)2-2054-8207 E-mail: sales@hpkr.co.kr