## Photodiode arrays with amplifiers

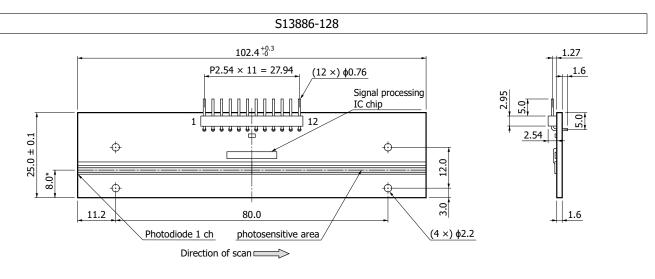

S13885-128/-256, S13886-128

# Photodiode arrays combined with signal processing IC for X-ray detection

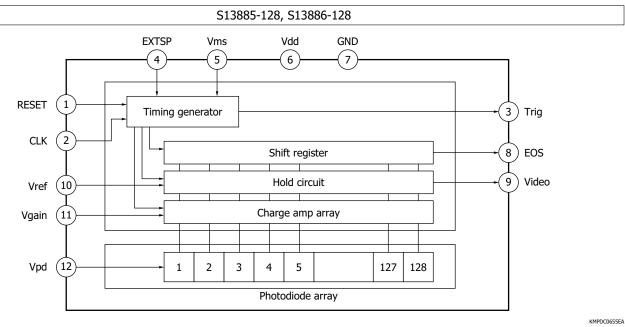

The S13885-128/-256, S13886-128 are Si photodiode arrays combined with a signal processing IC chip. Improvement in the signal processing IC chip has achieved higher sensitivity compared to the previous products (S11865/S11866 series). The signal processing IC chip is formed by CMOS process and incorporates a timing generator, shift register, charge amplifier array, clamp circuit and hold circuit, making the external circuit configuration simple. A long and narrow image sensor can be configured by arranging multiple arrays in a row.

## Features

- Data rate: 1 MHz max.

- Element pitch: 3 types available S13885-128: 0.4 mm pitch × 128 ch S13885-256: 0.2 mm pitch × 256 ch S13886-128: 0.8 mm pitch × 128 ch

- 3.3 V power supply operation

- Simultaneous integration method by using a charge amplifier array

- Low dark current due to zero-bias photodiode operation

- Integrated clamp circuit allows low noise and wide dynamic range.

- Integrated timing generator allows operation at two different pulse timings.

- Detectable energy range: 30 k to 100 keV

- Types with phosphor sheet affixed on the photosensitive area are available for X-ray detection (S13885-128G/-256G, S13886-128G)

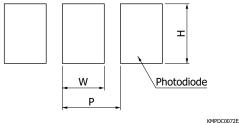

## - Structure

| Parameter             | Symbol*1 | S13885-128  | S13885-256 | S13886-128 | Unit |  |

|-----------------------|----------|-------------|------------|------------|------|--|

| Element pitch         | Р        | 0.4         | 0.2        | 0.8        | mm   |  |

| Element width         | W        | 0.3         | 0.1        | 0.7        | mm   |  |

| Element height        | Н        | 0.6         | 0.3        | 0.8        | mm   |  |

| Number of elements    | -        | 128         | 256        | 128        | -    |  |

| Effective area length | -        | 51.2        | 51.2       | 102.4      | mm   |  |

| Board material        | -        | Glass epoxy |            |            |      |  |

\*1: Refer to following figure.

## - Enlarged drawing of photosensitive area

## Applications

Line sensors for X-ray detection

Long and narrow line sensors

1

## Absolute maximum ratings (Ta=25 °C unless otherwise noted)

| Parameter                           | Symbol   | Value        | Unit |

|-------------------------------------|----------|--------------|------|

| Supply voltage                      | Vdd      | -0.3 to +4.2 | V    |

| Reference voltage                   | Vref     | -0.3 to +4.2 | V    |

| Photodiode voltage                  | Vpd      | -0.3 to +4.2 | V    |

| Gain selection terminal voltage     | Vgain    | -0.3 to +4.2 | V    |

| Master/slave selection voltage      | Vms      | -0.3 to +4.2 | V    |

| Clock pulse voltage                 | V(CLK)   | -0.3 to +4.2 | V    |

| Reset pulse voltage                 | V(RESET) | -0.3 to +4.2 | V    |

| External start pulse voltage        | V(EXTSP) | -0.3 to +4.2 | V    |

| Operating temperature* <sup>2</sup> | Topr     | -5 to +60    | °C   |

| Storage temperature* <sup>2</sup>   | Tstg     | -10 to +70   | °C   |

\*2: No dew condensation

When there is a temperature difference between a product and the surrounding area in high humidity environment, dew condensation may occur on the product surface. Dew condensation on the product may cause deterioration in characteristics and reliability.

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

## Recommended terminal voltage (Ta=25 °C)

| Parameter                      | Symbol                            | Min.     | Тур.       | Max.      | Unit       |   |

|--------------------------------|-----------------------------------|----------|------------|-----------|------------|---|

| Supply voltage                 |                                   | Vdd      | 3.0        | 3.3       | 3.6        | V |

| Reference voltage              |                                   | Vref     | Vdd - 1.0  | Vdd - 0.8 | Vdd - 0.6  | V |

| Photodiode voltage             |                                   | Vpd      | -          | Vref      | -          | V |

| Gain selection terminal        | Gain selection terminal High gain |          | Vdd - 0.25 | Vdd       | Vdd + 0.25 | V |

| voltage                        | Low gain                          | Vgain    | 0          | -         | 0.25       | V |

| Master/days calestian valtage  | High level*3                      | Vms      | Vdd - 0.25 | Vdd       | Vdd + 0.25 | V |

| Master/slave selection voltage | Low level*4                       | VIIIS    | 0          | -         | 0.25       | V |

| Clock pulse voltage            | High level                        |          | Vdd - 0.25 | Vdd       | Vdd + 0.25 | V |

| CIOCK pulse vollage            | Low level                         | V(CLK)   | 0          | -         | 0.25       | V |

|                                | High level                        |          | Vdd - 0.25 | Vdd       | Vdd + 0.25 | V |

| Reset pulse voltage            | Low level                         | V(RESET) | 0          | -         | 0.25       | V |

| External start pulse veltage   | High level                        |          | Vdd - 0.25 | Vdd       | Vdd + 0.25 | V |

| External start pulse voltage   | Low level                         | V(EXTSP) | 0          | -         | 0.25       | V |

\*3: Parallel

\*4: Serial at 2nd or later stages

## Electrical characteristics [Ta=25 °C, Vdd=3.3 V, V(CLK)=V(RESET)=3.3 V]

| Para                                | meter             | Symbol | Min. | Тур.  | Max. | Unit     |

|-------------------------------------|-------------------|--------|------|-------|------|----------|

| Clock pulse frequency               | *5                | f(CLK) | 40   | -     | 4000 | kHz      |

| Line rate <sup>*6</sup>             | S13885/S13886-128 | LR     | -    | -     | 7568 | lines/s  |

|                                     | S13885-256        |        | -    | -     | 3844 | iiiies/s |

| Output impedance                    |                   | Zo     | -    | 3     | -    | kΩ       |

| Current concumption                 | S13885/S13886-128 | Ic     | -    | 36    | -    | m۸       |

| Current consumption                 | S13885-256        |        | -    | 72    | -    | mA       |

| Charge amplifier feedback High gain |                   | Cf     | -    | 0.125 | -    | nE       |

| capacitance                         | Low gain          | U U    | -    | 0.25  | -    | pF       |

\*5: Video data rate is 1/4 of f(CLK).

\*6: The values depend on the clock pulse frequency.

## Electrical and optical characteristics [Ta=25 °C, Vdd=3.3 V, V(CLK)=V(RESET)=3.3 V, Vgain=3.3 V (high gain), 0 V (low gain)]

| Daram                          | Parameter   |         | S13885-128G |            | S1   | S13885-256G |            | S13886-128G |            | Unit       |      |                |

|--------------------------------|-------------|---------|-------------|------------|------|-------------|------------|-------------|------------|------------|------|----------------|

| Parameter                      |             | Symbol  | Min.        | Тур.       | Max. | Min.        | Тур.       | Max.        | Min.       | Тур.       | Max. | Unit           |

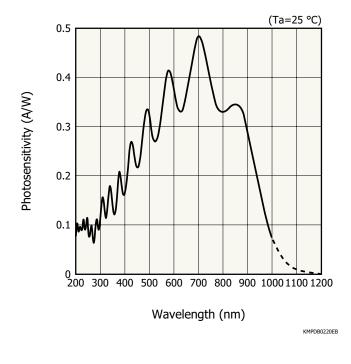

| Spectral response              | range       | λ       | 200 to 1000 |            | 20   | 200 to 1000 |            | 200 to 1000 |            | 0          | nm   |                |

| Peak sensitivity wa            | avelength*7 | λр      | -           | 720        | -    | -           | 720        | -           | -          | 720        | -    | nm             |

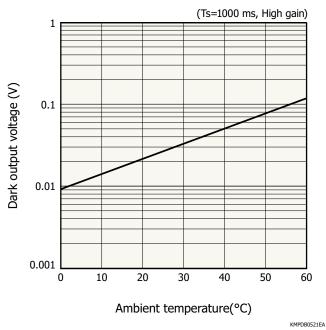

| Dark output                    | High gain   | VD      | -           | 0.02       | 0.2  | -           | 0.02       | 0.2         | -          | 0.02       | 0.2  | mV             |

| voltage*8                      | Low gain    | VU      | -           | 0.01       | 0.1  | -           | 0.01       | 0.1         | -          | 0.01       | 0.1  | IIIV           |

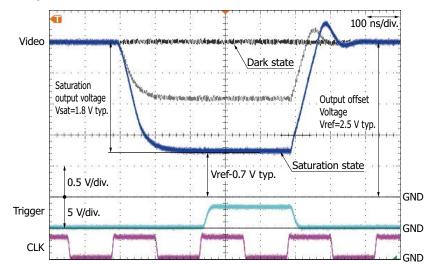

| Saturation output voltage      |             | Vsat    | Vref - 1.0  | Vref - 0.7 | -    | Vref - 1.0  | Vref - 0.7 | -           | Vref - 1.0 | Vref - 0.7 | -    | V              |

|                                | High gain   | Pin_sat | -           | 0.3        | 0.4  | -           | 1.8        | 2.3         | -          | 0.1        | 0.13 | ml             |

| exposure*7 *9                  | Low gain    |         | -           | 0.6        | 0.8  | -           | 3.6        | 4.5         | -          | 0.2        | 0.26 | $mlx \cdot s$  |

| Photosensitivity*7 *9          | High gain   | Sw      | 4800        | 6000       | -    | 800         | 1000       | -           | 14080      | 17600      | -    |                |

| Photosensitivity               | Low gain    |         | 2400        | 3000       | -    | 400         | 500        | -           | 7040       | 8800       | -    | $V/lx \cdot s$ |

| Photoresponse nonuniformity*10 |             | PRNU    | -           | -          | ±10  | -           | -          | ±10         | -          | -          | ±10  | %              |

| Readout noise*11               | High gain   | Nread   | -           | 1.0        | 1.5  | -           | 0.6        | 0.9         | -          | 1.7        | 2.6  | mV rms         |

|                                | Low gain    | INIEdu  | -           | 0.6        | 0.9  | -           | 0.4        | 0.6         | -          | 1.0        | 1.5  | 1110 11115     |

| Output offset volta            | age*12      | Voffset | -           | Vref       | -    | -           | Vref       | -           | -          | Vref       | -    | V              |

\*7: Measured without phosphor sheet

\*8: Integration time ts=1 ms

\*9: Measured with a 2856 K tungsten lamp

\*10: Photoresponse nonuniformity (PRNU) is the output nonuniformity that occurs when the photosensitive area is uniformly illuminated by light which is approx. 50% of the saturation level. PRNU is defined as follows: PRNU =  $\Delta X/X \times 100$  [%]

X: average output of all elements,  $\Delta X$ : difference between X and the maximum or minimum output, whichever is larger.

\*11: Video data rate=1 MHz, dark state, ts=1 ms

\*12: Video output is negative-going output with respect to the output offset voltage.

## Output waveform of one element

## Spectral response (typical example)

When silicone resin is applied (for attaching a fluorescent screen)

KMPDB0421EA

4

When the fluorescent screen is attached, the spectral response becomes smooth due to the effects of the adhesive resin.

Dark output voltage vs. ambient temperature (typical example)

## Block diagram

## Photodiode arrays with amplifiers

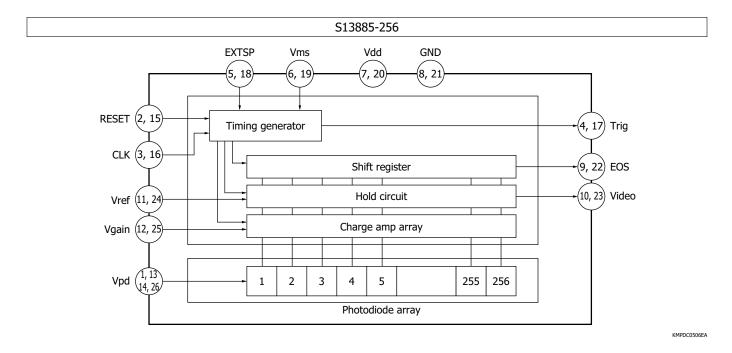

Timing chart

KMPDC0651EB

| Parameter                        | Symbol               | Min. | Тур. | Max.  | Unit |

|----------------------------------|----------------------|------|------|-------|------|

| Clock pulse width                | tpw(CLK)             | 250  | -    | 25000 | ns   |

| Clock pulse rise/fall times      | tr(CLK), tf(CLK)     | 0    | 20   | 30    | ns   |

| Reset pulse width 1              | tpw(RESET1)          | 25   | -    | -     | CLK  |

| Reset pulse width 2              | tpw(RESET2)          | 40   | -    | -     | CLK  |

| Reset pulse rise/fall times      | tr(RESET), tf(RESET) | 0    | 20   | 30    | ns   |

| Clock pulse-reset pulse timing 1 | t1                   | -20  | 0    | 20    | ns   |

| Clock pulse-reset pulse timing 2 | t2                   | -20  | 0    | 20    | ns   |

1. The internal timing circuit starts operation at the falling edge of CLK immediately after a RESET pulse goes low.

2. When the falling edge of this CLK is counted as 1 clock, the video signal of the 1st channel appears between 18.5 clocks and 20.5 clocks. Subsequent video signals appear every 4 clocks.

3. The trigger pulse for the 1st channel rises at a timing of 19.5 clocks and then rises every 4 clocks. The rising edge of each trigger pulse is the recommended timing for data acquisition.

4. Signal charge integration time equals [the high period of a RESET pulse - 22 clocks]. The charge integration starts at the fall of the 30th clock after the rise of the RESET pulse and ends at the fall of the 8th clock after the fall of the RESET pulse. After the RESET pulse next changes from high to low, signals integrated within this period are sequentially read out as time-series signals by the shift register operation. The rise and fall of a RESET pulse must be synchronized with the rise of a CLK pulse, but the rise of a RESET pulse must be set outside the video output period. One cycle of RESET pulses cannot be set shorter than the time equal to [16.5 + 4 × N (number of elements)] clocks.

5. The video signal after an EOS signal output becomes a high impedance state, and the video output will be indefinite.

KMPDA0615EA

KMPDA0616EA

7

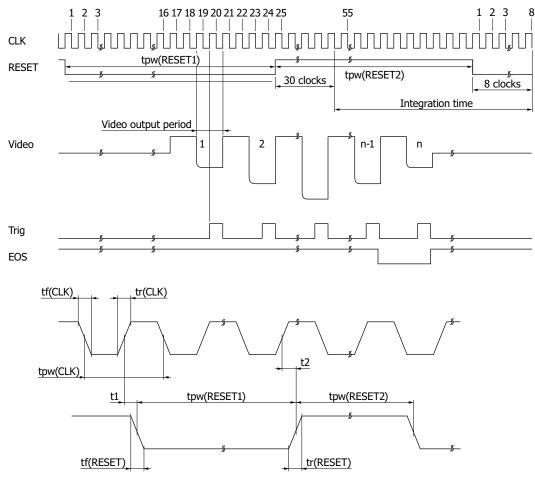

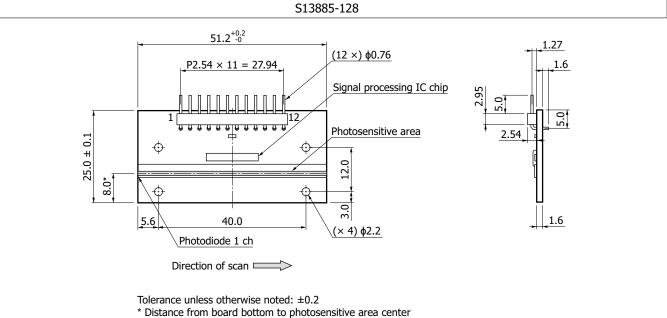

## Dimensional outlines (unit: mm)

Board: G10 glass epoxy

Connector: PRECI-DIP DURTAL 800-10-012-20-001101

S13885-256 51.2<sup>+0.2</sup> (26 ×) 🗆 0.64 34.02 2.54 2.28  $P2.54 \times 12 = 30.48$ 1.2 6.0 10.0 (× 4) ¢2.2 6.9 25 1 Photosensitive 5  $40.0 \pm 0.15$ 2 26 area 6.6 ~i  $\odot$ £ CMOSI CMOS2 17.0 8.0\* Ć 3.0 5.6 40.0 1.6 Photodiode 1 ch Signal processing IC chip

Direction of scan

Tolerance unless otherwise noted: ±0.2

\* Distance from board bottom to photosensitive area center

Board: G10 glass epoxy

Connector: JAE (Japan Aviation Electronics Industry, Limited) PS-26PE-D4LT1-PN1

## Photodiode arrays with amplifiers

Tolerance unless otherwise noted:  $\pm 0.2$  \* Distance from board bottom to photosensitive area center

Board: G10 glass epoxy Connector: PRECI-DIP DURTAL 800-10-012-20-001101

KMPDA0617EA

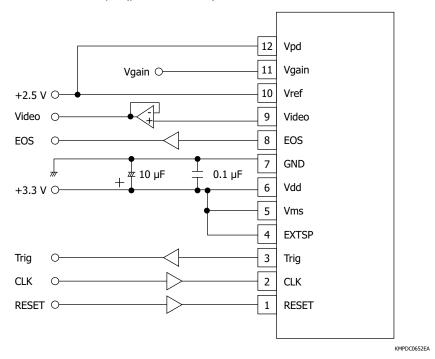

## Pin connections

|         | S13885-128, S13886-128 |                                 |                                 |  |  |  |  |  |

|---------|------------------------|---------------------------------|---------------------------------|--|--|--|--|--|

| Pin no. | Symbol                 | Name                            | Note                            |  |  |  |  |  |

| 1       | RESET                  | Reset pulse                     | Pulse input                     |  |  |  |  |  |

| 2       | CLK                    | Clock pulse                     | Pulse input                     |  |  |  |  |  |

| 3       | Trig                   | Trigger pulse                   | Positive-going pulse output     |  |  |  |  |  |

| 4       | EXTSP                  | External start pulse            | Pulse input                     |  |  |  |  |  |

| 5       | Vms                    | Master/slave selection voltage  | Voltage input                   |  |  |  |  |  |

| 6       | Vdd                    | Supply voltage                  | Voltage input                   |  |  |  |  |  |

| 7       | GND                    | Ground                          |                                 |  |  |  |  |  |

| 8       | EOS                    | End of scan                     | Negative-going pulse output     |  |  |  |  |  |

| 9       | Video                  | Video output                    | Negative-going output from Vref |  |  |  |  |  |

| 10      | Vref                   | Reference voltage               | Voltage input                   |  |  |  |  |  |

| 11      | Vgain                  | Gain selection terminal voltage | Voltage input                   |  |  |  |  |  |

| 12      | Vpd                    | Photodiode voltage              | Voltage input                   |  |  |  |  |  |

|         | S13885-256 |         |       |                                |                                 |  |  |

|---------|------------|---------|-------|--------------------------------|---------------------------------|--|--|

| Pin no. | CMOS1      | Pin no. | CMOS2 | Name                           | Note                            |  |  |

| 1       | Vpd        | 14      | Vpd   | Photodiode voltage             | Voltage input                   |  |  |

| 2       | RESET      | 15      | RESET | Reset pulse                    | Pulse input                     |  |  |

| 3       | CLK        | 16      | CLK   | Clock pulse                    | Pulse input                     |  |  |

| 4       | Trig       | 17      | Trig  | Trigger pulse                  | Positive-going pulse output     |  |  |

| 5       | EXTSP      | 18      | EXTSP | External start pulse           | Pulse input                     |  |  |

| 6       | Vms        | 19      | Vms   | Master/slave selection voltage | Voltage input                   |  |  |

| 7       | Vdd        | 20      | Vdd   | Supply voltage                 | Voltage input                   |  |  |

| 8       | GND        | 21      | GND   | Ground                         |                                 |  |  |

| 9       | EOS        | 22      | EOS   | End of scan                    | Negative-going pulse output     |  |  |

| 10      | Video      | 23      | Video | Video output                   | Negative-going output from Vref |  |  |

| 11      | Vref       | 24      | Vref  | Reference voltage              | Voltage input                   |  |  |

| 12      | Vgain      | 25      | Vgain | Gain selection voltage         | Voltage input                   |  |  |

| 13      | Vpd        | 26      | Vpd   | Photodiode voltage             | Voltage input                   |  |  |

## Gain selection terminal voltage setting

Vdd: High gain (Cf=0.125 pF) GND: Low gain (Cf=0.25 pF)

## Setting for each readout method

S13885-128, S13886-128

#### Set to A in the table below in most cases.

To serially read out signals from two or more sensors linearly connected, set the 1st sensor to A and the 2nd or later sensors to B. The CLK and RESET pulses should be shared with each sensor and the video output terminal of each sensor connected together.

Connection example (parallel readout)

Note: When making a serial connection with two or more sensors or when connecting the sensor with a long cable, connect a highimpedance amplifier near the sensor if necessary.

| Setting | Readout method                                               | Vms | EXTSP                          |

|---------|--------------------------------------------------------------|-----|--------------------------------|

| A       | All stages of parallel readout, serial readout at 1st sensor | Vdd | Vdd                            |

| В       | Serial readout at 2nd and later sensors                      | GND | Preceding sensor EOS is input. |

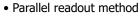

### S13885-256

Signals of channels 1 through 128 are output from CMOS1, while signals of channels 129 through 256 are output from CMOS2. The following two readout methods are available.

#### (1) Serial readout method

CMOS1 and CMOS2 are connected in serial and the signals of channels 1 through 256 are sequentially read out from one output line. Set CMOS1 as in "A" in the table below, and set CMOS2 as in "B". Use a common CLK for CMOS1 and CMOS2. Likewise, use a common RESET for CMOS1 and CMOS2. Connect the video output terminals to a single line.

#### (2) Parallel readout method

128 channel signals are output in parallel respectively from the output lines of CMOS1 and CMOS2. Set both CMOS1 and CMOS2 as in "A" in the table below.

### Connection examples

## Serial readout method

KMPDC0654EA

CMOS1

2 RESET (1)

3 CLK (1)

4 Trig (1)

6 Vms (1)

10 Video (1)

CMOS2

15 RESET (2)

16 CLK (2)

17 Trig (2)

19 Vms (2) 20 Vdd

21 GND

24 Vref

25 Vgain

26 Vpd

22 EOS (2)

23 Video (2)

18 EXTSP (2)

7 Vdd

8 GND

12 Vgain

13 Vpd

14 Vpd

9 EOS (1)

11 Vref

5 EXTSP (1)

1 Vpd

Note: When making a serial connection with two or more sensors or when connecting the sensor with a long cable, connect a highimpedance amplifier near the sensor if necessary.

| Setting | Vms | EXTSP                          |

|---------|-----|--------------------------------|

| A       | Vdd | Vdd                            |

| В       | GND | Preceding sensor EOS is input. |

## Readout circuit

Apply pulse signals that meet the required conditions to the input terminals. Video output should be amplified by an op amp that is connected close to the sensor.

## Precautions

- (1) The signal processing IC chip is protected against static electricity. However, in order to prevent possible damage to the IC chip, take electrostatic countermeasures such as grounding yourself, as well as workbench and tools. Also protect the IC chip from surge voltages from peripheral equipment.

- (2) Gold wires for wire bonding are very thin, so they easily break if subjected to mechanical stress. The signal processing IC chip and wire bonding are covered with resin for protection, but make sure they do not get scratched. Never touch these portions or the photodiode array chip affixed with the phosphor sheet. Excessive force, if applied, may break the wires or cause malfunction. Blow air to remove dust or debris if it gets on the protective resin. Never wash them with solvent. Signals may not be obtained if dust or debris is left or a scratch is made on the protective resin or the phosphor sheet or if the signal processing IC chip or photodiode array chip is nicked.

- (3) The photodiode array characteristics may deteriorate when operated at high humidity, so put it in a hermetically sealed enclosure or case. When installing the photodiode array with amplifier on a board, be careful not to cause the board to warp.

- (4) The characteristics of the signal processing IC chip deteriorate if exposed to X-rays. So use a lead shield which is at least 1 mm larger all around than the signal processing IC chip. The 1 mm margin may not be sufficient depending on the incident angle of Xrays. Provide an even larger shield as long as it does not cover the photodiode photosensitive area. Since the optimal shield thickness depends on the operating conditions, calculate it by taking the attenuation coefficient of lead into account.

- (5) The sensitivity of the photodiode array chip decreases if continuously exposed to X-rays. The extent of this sensitivity decrease differs depending on the X-ray irradiation conditions.

- (6) When a scintillator is mounted on a photodiode array chip, increased photoresponse nonuniformity caused by the intrusion of bubbles due to adhesive resin shortage is a concern. Make sure that the adhesive resin covers the entire photodiode array chip. The photodiode array chip is hard but at the same time fragile and easily chipped. When mounting a scintillator on a photodiode array chip, be careful not to physically damage the chip with a sharp object or the like.

## Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- Disclaimer

- · Unsealed products

- Image sensors

Information described in this material is current as of May 2022.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use. Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

##

## www.hamamatsu.com

#### HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81)53-434-3311, Fax: (81)53-434-5184

U.S.A.: HAMAMATSU CORPORATION: 360 Foothill Road, Bridgewater, NJ 08807, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218 E-mail: usa@hamamatsu.com Germany: HAMAMATSU PHOTONICS DEUTSCHLAND GMBH: Arzbergerstr. 10, 82211 Herrsching am Ammersee, Germany, Telephone: (4)9152-375-0, Fax: (4)9152-255-8 E-mail: info@hamamatsu.de France: HAMAMATSU PHOTONICS FRANCE S.A.R.L: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (3)1 69 53 71 00, Fax: (33)1 69 53 71 10 E-mail: info@hamamatsu.de Inited Kingdom: HAMAMATSU PHOTONICS INL LIMITED: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire Al 7 18/W, UK, Telephone: (4)1707-234888, Fax: (44)1707-325777 E-mail: info@hamamatsu.co.uk North Europe: HAMAMATSU PHOTONICS NORDEN AB: Torshamnsgatan 35 16440 Kista, Sweden, Telephone: (46)8-509 031 01 E-mail: info@hamamatsu.se United initiation in the initiation of the in